Comprender el acoplamiento electromagnético (EM) entre varios elementos de un dispositivo semiconductor de alta frecuencia es vital para cumplir con las especificaciones de diseño y garantizar un funcionamiento confiable en el campo. Estas interacciones EM incluyen no sólo el chip de silicio sino que también se extienden al paquete que lo encierra. Sin embargo, es posible que solo hacia el final de un proyecto el diseñador de circuitos integrados o de sistemas pueda crear y simular modelos EM que incluyan tanto los metales en el troquel como las capas del paquete. No es raro encontrar que la inclusión de las capas del paquete con el modelo de metales en el troquel provoca una degradación en el rendimiento que puede provocar la violación de las especificaciones. Para evitar esto, Ansys proporciona una solución que puede agregar fácilmente capas de paquete a una pila de metal de tecnología de silicio para extraer modelos completos con capas de paquete y de silicio en las primeras etapas del proceso de diseño.

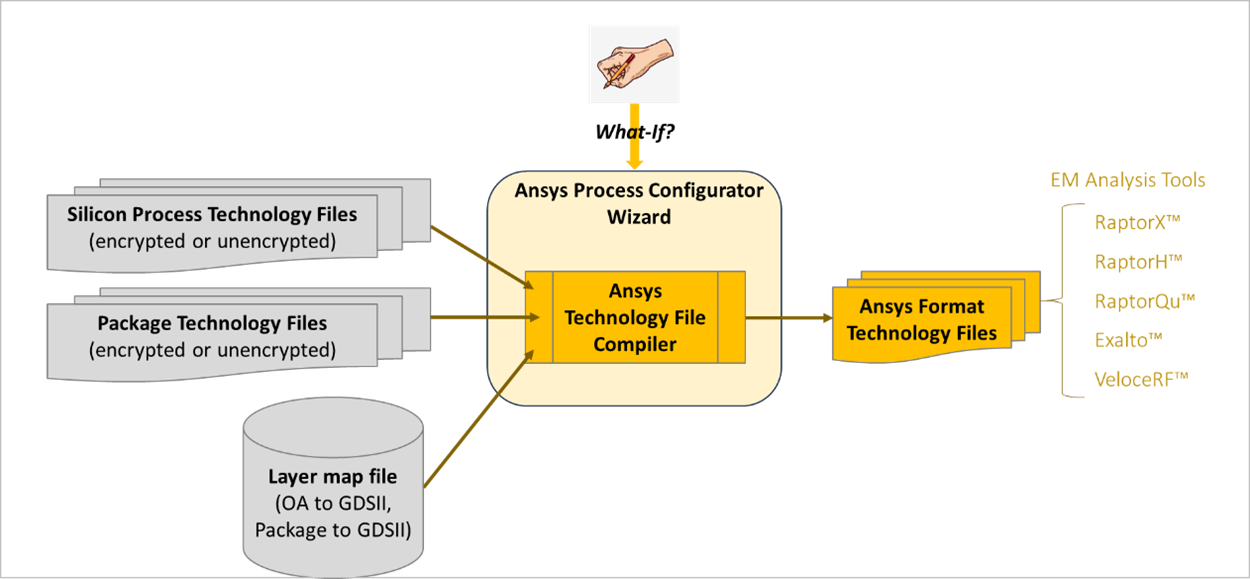

El conjunto de herramientas de análisis electromagnético en chip de Ansys opera en diseños de circuitos integrados en la etapa de diseño anterior al LVS (Ansys RaptorX™) y la etapa de aprobación posterior a LVS (Ansys Exalto™). El análisis del chip puede incluir partes del diseño del paquete y/o capas del paquete para extraer un modelo EM completo que se puede simular con un simulador de circuito SPICE. Las herramientas Ansys se basan en información precisa sobre la tecnología del proceso de interconexión utilizada en la fabricación de cada capa. Las fundiciones de silicio proporcionan la información del proceso en varios formatos, incluidos manuales de reglas de diseño (DRM) y archivos de tecnología, como archivos iRCX, ITF y ICT, que pueden estar cifrados o sin cifrar. El proceso para capturar la acumulación de tecnología compila una colección de archivos de tecnología en formato Ansys al mapear la información de tecnología de proceso proporcionada por la fundición en información de diseño físico en formato de flujo OpenAccess o GDSII (consulte la Figura 1). Estos archivos de tecnología compilados también son compatibles con otras herramientas EM en chip de Ansys, incluidas Ansys VeloceRF™ (síntesis de diseño de dispositivo inductivo) y Ansys RaptorQu™ (para diseño cuántico superconductor).

RaptorX es un solucionador electromagnético optimizado para silicio y viene con un asistente muy útil llamado Process Configurator que facilita la creación y modificación de archivos de tecnología Ansys, incluso para configuraciones complejas de paquetes de chips. Como se muestra en la Figura 1, Process Configurator crea archivos de tecnología Ansys que pueden contener solo la pila de metal de fundición o pueden contener la pila de metal de fundición más capas de paquete adicionales seleccionadas. La entrada al asistente del Configurador de procesos para la acumulación de metal de fundición es la información del proceso proporcionada por la fundición. Si es necesario coextraer las capas de matriz y paquete, entonces también se debe incluir la información de la capa de paquete para las capas de interés.

Si el archivo de tecnología de fundición no está cifrado, o la información de la capa del paquete no está cifrada, el asistente del Configurador de procesos le permitirá explorar varios escenarios hipotéticos relacionados con el proceso editando las propiedades de las capas del troquel y/o del paquete y compilando diferentes versiones. de los archivos de tecnología Ansys. El Configurador de procesos permite a los diseñadores agregar o quitar sustratos, placas posteriores, conductores, dieléctricos y vías, incluidas las vías a través de silicio (TSV). Las propiedades tecnológicas que se pueden editar con Process Configurator son el espesor del metal, la conductividad del metal, el espesor dieléctrico y la constante dieléctrica. Para completar los archivos de tecnología Ansys, el compilador también requiere el archivo de mapa de capas de flujo GDS y la información de mapeo de capas.

Algunos ejemplos de modificación de una tecnología no cifrada para experimentos hipotéticos incluyen:

- Modificar el espesor y las propiedades del sustrato para explorar los efectos del acoplamiento a través del sustrato.

- Agregar TSV en una pila 3DIC exploratoria

- configurar un archivo de tecnología para la tecnología Wafer-on-Wafer (WoW)

agregar capas de paquetes para ver su efecto en el dispositivo EM, como se mostrará en el siguiente ejemplo

Los archivos de entrada y la información para Process Configurator se pueden procesar utilizando una interfaz de usuario y un script de comando en modo por lotes. Los resultados de Process Configurator son los archivos compilados de tecnología de procesos Ansys utilizados por el conjunto de herramientas Ansys EM. El Configurador de procesos tiene la capacidad muy útil de visualizar una sección transversal de tecnología, lo que facilita verificar la secuencia correcta y la conectividad de las capas de tecnología. Las propiedades de la capa de tecnología no cifrada, como el espesor, la resistividad y la constante dieléctrica, también se muestran en el visor de secciones transversales. Si la tecnología está cifrada, el visor de secciones transversales muestra la secuencia de capas y la conectividad, pero los espesores de las capas no están a escala y no se informan las propiedades del material.

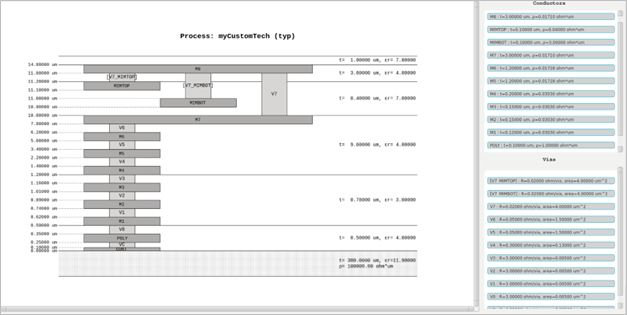

La Figura 2 a continuación muestra una pila de un archivo de tecnología de ejemplo ficticio. El panel izquierdo muestra las características del sustrato en la capa inferior, la altura de la capa acumulada a partir del sustrato, la capa y los nombres de la izquierda, y el espesor dieléctrico y la constante dieléctrica (er) A la derecha. La sección Conductor en el panel derecho enumera los conductores con su espesor y resistividad (r), y la sección Vías muestra la resistencia y el área de la vía.

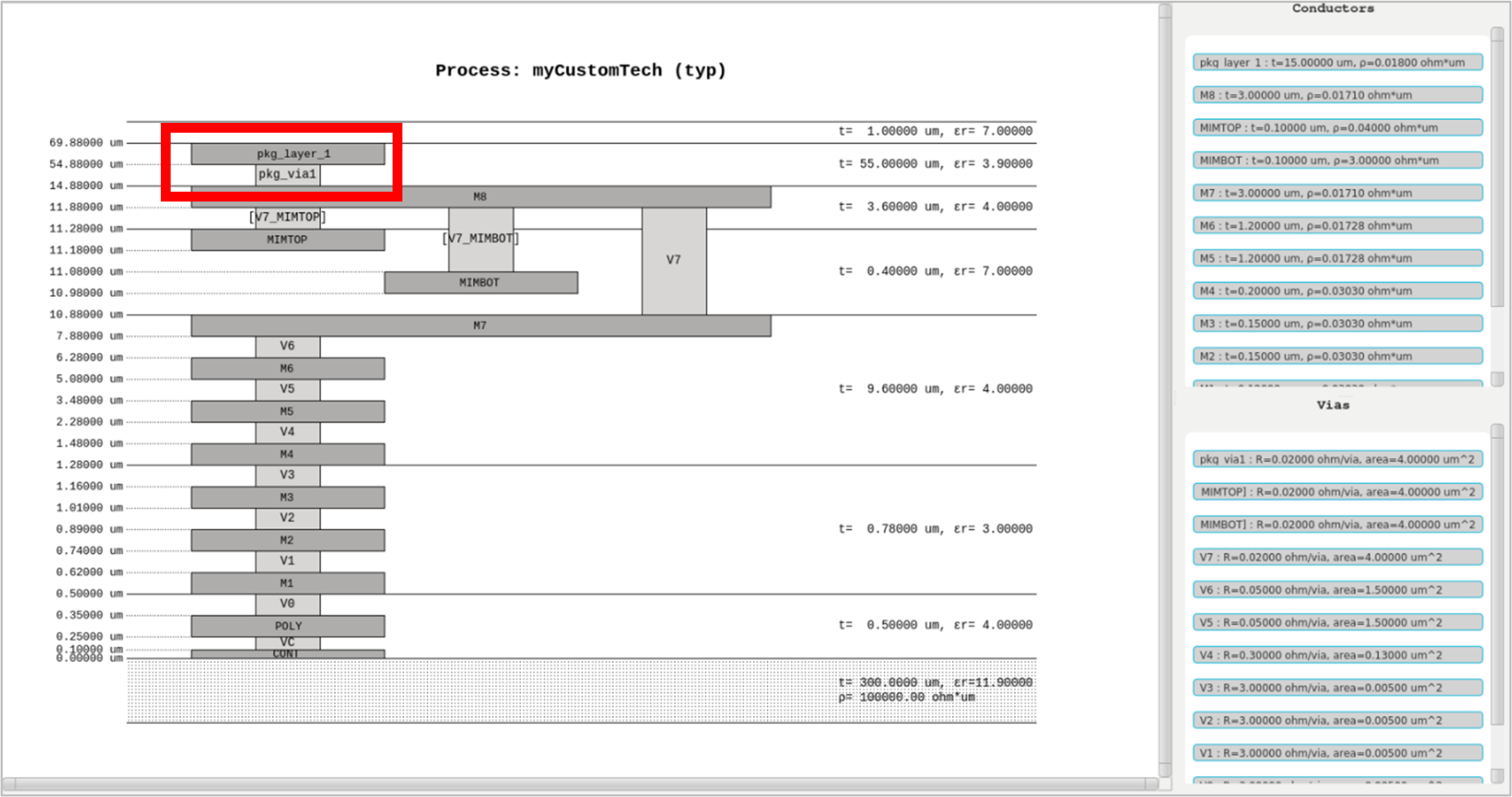

El cuadro rojo en la Figura 3 a continuación resalta una vía y una capa de paquete que se agregaron a la pila. Esta acumulación, con la capa de paquete y la vía incluidas, se utilizó para los resultados de simulación descritos en los siguientes párrafos que muestran cómo la capa de paquete puede afectar el rendimiento de un dispositivo EM.

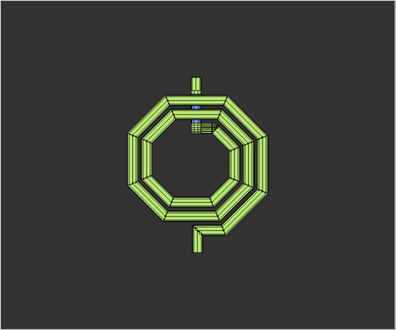

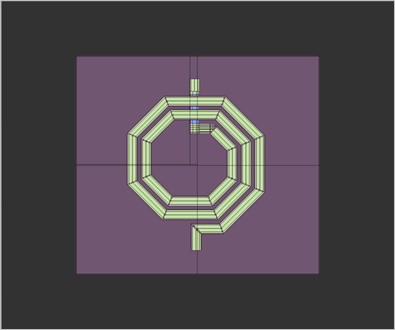

Para ilustrar cómo se puede utilizar Process Configurator para explorar el efecto de un paquete en un chip, creamos un ejemplo de diseño simple: consta de un dispositivo EM (un inductor en espiral octogonal de un solo extremo) que se extrajo usando RaptorX. Luego, el modelo eléctrico resultante se simuló en un simulador de circuito de nivel SPICE para analizar el rendimiento primero con y luego nuevamente sin una capa de paquete colocada encima. La Figura 4 a continuación muestra la malla física de RaptorX para el inductor sin la capa de paquete.

A continuación, se utilizó el mismo inductor, pero encima se colocó un rectángulo de la capa del paquete. La Figura 5 a continuación muestra la malla RaptorX del inductor con la capa de paquete incluida.

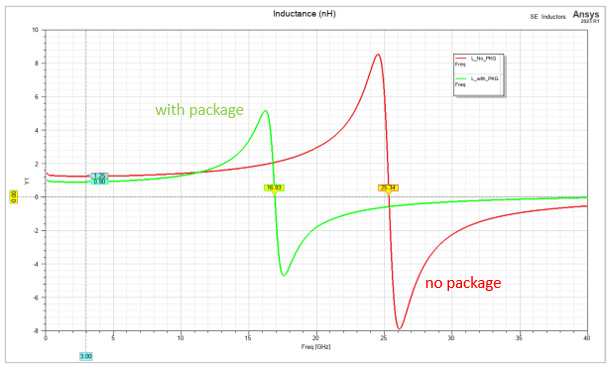

RaptorX generó un modelo de parámetro S para cada inductor, que luego se simuló para determinar la inductancia y el factor de calidad en un rango de frecuencia. La Figura 6 muestra la inductancia de los dos inductores trazada en frecuencia. La comparación del gráfico de inductancia a 3 GHz para la capa del paquete incluida (verde) muestra una disminución del 28 % en la inductancia y del 33 % en la frecuencia de resonancia versus los resultados de la simulación para el modelo sin la capa del paquete (rojo).

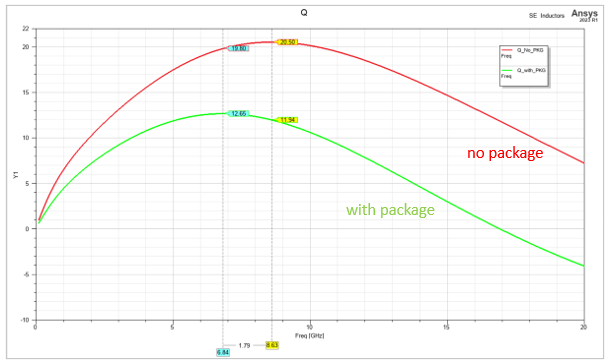

En la Figura 7 a continuación, el factor de calidad (Q) de los dos inductores se representa en función de la frecuencia. La comparación del gráfico de simulación de Q para la capa de paquete incluida (verde) muestra una disminución del 38 % en el valor de Q máximo y una disminución del 21 % en la frecuencia máxima de Q en comparación con los resultados de la simulación para el modelo sin la capa de paquete (rojo).

En resumen, estos resultados de simulación ilustran los marcados cambios en el comportamiento del dispositivo que se observan cuando se incluyen capas de paquetes en una simulación. Modelar capas de paquetes junto con metales en el troquel puede revelar una degradación en el rendimiento que puede violar una especificación o provocar que el dispositivo falle. Ansys ha desarrollado el Configurador de procesos para que a los diseñadores de circuitos integrados y sistemas les resulte muy fácil capturar incluso las configuraciones de embalaje multicapa más complejas y facilitar una experimentación rápida. Fomenta un enfoque de desplazamiento a la izquierda con exploración temprana de hipótesis para ayudar a los diseñadores a encontrar la mejor solución posible para optimizar su producto final y evitar sorpresas en las últimas etapas.

Lea también

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/eda/340090-will-the-package-kill-my-high-frequency-chip-design/