Probablemente esté familiarizado con el acrónimo PPA, que significa Potencia/Rendimiento/Área. A veces es PPAC, donde C es para el costo, ya que el costo implica más que solo el área. Por ejemplo, ¿sabía que agregar una capa de metal adicional a un chip aumenta drásticamente el costo, a veces en millones de dólares? Requiere un mínimo de dos máscaras (interconexión y vías) más todos los pasos del proceso asociados adicionales. Y las capas de interconexión normalmente vienen en pares, verticales y horizontales, por lo que normalmente son cuatro máscaras.

Hay muchas aportaciones para optimizar PPAC, y una de ellas importante es el diseño del árbol del reloj. El reloj puede consumir mucha energía y gran parte de la interconexión, y obviamente afecta el rendimiento. El proceso de diseño del árbol del reloj generalmente se denomina Síntesis del árbol del reloj, generalmente abreviado como CTS. Siemens EDA publicó recientemente un libro blanco Técnicas de colocación y CTS para diseños informáticos de alto rendimiento.

Un desafío que enfrentan las herramientas EDA es que solo se obtiene la verdadera calidad de los resultados cuando se ha terminado el diseño. En la práctica, esto significa que las herramientas deben utilizar el pesimismo para proteger los resultados o aumentar la precisión al tener una correlación mucho mejor entre la herramienta en uso y los resultados finales.

El documento técnico analiza cómo resolver los desafíos de ubicación y árbol de reloj en diseños de HPC utilizando la solución de implementación digital Aprisa, ya que estos pasos son fundamentales para lograr las métricas de rendimiento deseadas durante el lugar y la ruta. Mientras que la mayoría de las otras herramientas de ubicación y ruta requieren esperar hasta la optimización posterior a la ruta para descubrir la verdadera calidad de los resultados, Aprisa ofrece a los usuarios una excelente correlación durante toda la implementación de ubicación y ruta, lo que permite a los diseñadores ganar confianza en los resultados mucho antes. en el flujo en las etapas de colocación y síntesis del árbol de reloj (CTS). Aprisa es ideal para ayudar a los diseñadores a implementar innovaciones en circuitos integrados HPC con mayor rapidez.

En caso de que no conozca los nombres de los productos de Siemens EDA (después de casi una década en Cadence, no los conocía), Aprisa es la solución de implementación digital de Siemens para diseños jerárquicos y a nivel de bloque. Bajo el capó, tiene una arquitectura centrada en la ruta para reducir el tiempo hasta el cierre del diseño, en parte trasladando las implicaciones de las decisiones tempranas en el proceso de diseño a esa fase, en lugar de esperar hasta que se complete el diseño para descubrir que tiene problemas que ya se habían resuelto. introducido anteriormente. Una clave para un flujo de implementación moderno es tener tiempos, extracción, DRC y más consistentes en todo el flujo.

Aprisa ofrece rendimiento, potencia y área (PPA) óptimos para nodos avanzados y cuenta con soporte completo para metodologías de diseño y optimización para lograr la menor potencia y el mayor rendimiento.

El documento técnico utiliza un diseño de ejemplo, un Arm Cortex-A76 de 5 nm que funciona a 2.75 GHz y utiliza 12 capas de metal para la interconexión. No tengo espacio aquí para entrar en detalles sobre el diseño; tendrás que leer el documento técnico para profundizar más.

El objetivo del ejercicio fue analizar el uso de 10 capas de metal versus 12 capas de metal (dije que las capas de interconexión generalmente ya vienen en pares). El análisis reveló que, para la opción de 10 capas, la frecuencia tendría que reducirse en un 9 por ciento para lograr el objetivo de potencia deseado. Sin embargo, resultó en importantes ahorros de costos para todo el proyecto. Obviamente, Aprisa no puede tomar la decisión por usted sobre si vale la pena alcanzar un rendimiento del 9% para reducir el costo.

El tema central del documento técnico es la síntesis del árbol de reloj (CTS), uno de los grandes desafíos en cualquier diseño de HPC. Aprisa admite un sesgo útil, comenzando con la optimización de la ubicación y continuando hasta la optimización de la ruta, para garantizar que se cumplan los diseños de objetivos de frecuencia desafiantes. Una fortaleza de la tecnología Aprisa CTS es que las compensaciones de empuje y tracción generadas durante la optimización de la ubicación se realizan durante la implementación del árbol de reloj.

Los relojes generalmente van a flip-flops, y una optimización que incluyen las bibliotecas celulares modernas son flip-flops de varios bits con un reloj común. Aprisa tiene la capacidad de fusionar o separar flip-flops multibit y clonar/declonar puertas de reloj integradas. Aprisa hace esto en función del tiempo, la ubicación física de las celdas y la criticidad de los caminos.

La optimización post-CTS en Aprisa incluye recuperación de congestión que recupera la congestión creada durante la síntesis del árbol de reloj. La recuperación de la congestión es un enfoque que tiene en cuenta el reloj y que no degrada el tiempo y, por lo tanto, reduce las iteraciones para optimizar la ubicación que de otro modo serían necesarias.

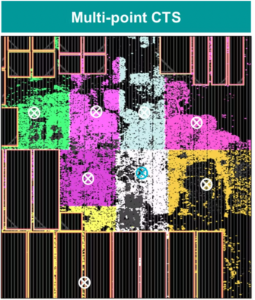

Aprisa admite diferentes tipos de estructuras de árbol de reloj, como árbol H, CTS multipunto y malla personalizada. El multipunto es el enfoque más popular para los diseños HPC y es el que se describe en el documento técnico.

¡Por supuesto, hay mucho más en un flujo de implementación que sintetizar el árbol del reloj! Pero CTS es una etapa crítica, especialmente para diseños HPC exigentes, porque hay muy poco margen de desviación para lograr el rendimiento deseado y así cumplir con los requisitos de PPA.

Aprisa está certificada por las principales fundiciones para los nodos más avanzados. Garantiza que todas las métricas de PPA estén cuidadosamente equilibradas para la implementación del diseño de HPC a través de árboles de reloj de alta calidad. Sin mencionar las tecnologías de colocación y enrutamiento que reducen la fricción del cierre de sincronización entre el bloque y el nivel superior durante el ensamblaje.

Una vez más, el documento técnico se puede descargar. haga clic aquí

Lea también

IA para el diseño de circuitos integrados analógicos de señal mixta personalizados

Optimización de los flujos de verificación física Shift-Left con Calibre

Reducción de la complejidad del diseño de sistemas electrónicos con IA

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/eda/siemens-eda/336466-placement-and-clocks-for-hpc/