RISC-V presenta una oportunidad única para que los diseñadores amplíen la microarquitectura con instrucciones personalizadas. Una posible aplicación es el filtrado de señales digitales utilizando respuesta de impulso finito (FIR) o filtros medianos, algoritmos potenciales para esquemas de demodulación de portadoras en sistemas de comunicaciones como 5G. Los equipos de aplicaciones de Codasip estudiaron el potencial para acelerar los filtros FIR y medianos en su núcleo L31 RISC-V, documentando su proceso de diseño para extender RISC-V y los resultados de la ejecución en su último documento técnico.

Una breve descripción general de FIR y filtros medianos

Los filtros FIR y de mediana buscan eliminar el ruido de una señal de entrada utilizando un conjunto de N muestras de la entrada en el dominio del tiempo. Ninguno de los filtros utiliza retroalimentación interna. Una cantidad razonable de muestras caben en una matriz de registros RISC-V, cambiando en cada reloj de muestra con la muestra más antigua saliendo de la matriz y la más nueva ingresando por el otro extremo.

El filtro FIR toma su nombre de su tiempo finito para establecerse en cero (si la señal de entrada es cero durante al menos N muestras consecutivas). Las muestras en el orden recibido se ponderan mediante multiplicación con coeficientes de filtro y se obtiene el resultado mediante una suma. El uso del conjunto de instrucciones RISC-V estándar da como resultado 2N-1 instrucciones, 2N cargas de memoria y aproximadamente N comparaciones y saltos dependiendo de la codificación del bucle for.

El filtro de mediana se basa en ordenar un conjunto de muestras en lugar de multiplicarlo. La secuencia de elementos ordenados da como resultado una mediana (la muestra en el medio) que se toma como resultado. Nuevamente, utilizando instrucciones RISC-V estándar, una clasificación generalmente requiere aproximadamente N·logN comparaciones aritméticas y aproximadamente el mismo número de operaciones de memoria.

Bloques de hardware personalizados para filtros digitales FIR (izquierda) y Mediana (derecha). Fuente: Codasip

Los equipos de Codasip investigaron la premisa de que las instrucciones personalizadas para cada filtro podrían acelerar la ejecución normal muestra por muestra una vez que cada FIFO se llena con N muestras: la "ventana de filtrado". Casualmente, la aceleración de los filtros FIR y mediano ocurre en tres ciclos de reloj RISC-V con diferentes pasos de ejecución en paralelo:

- Para el filtro FIR, el primer ciclo recupera los coeficientes del filtro, el segundo multiplica y suma, y el tercero escribe el resultado en el archivo de registro.

- Para el filtro de mediana, el primer ciclo elimina la muestra más antigua de la clasificación y la desplaza para cerrar la brecha, el segundo coloca la muestra más nueva y desplaza las muestras más grandes antes de insertarla, y el tercero extrae la mediana de la nueva clasificación.

Conceptos básicos de ampliar RISC-V con CodAL

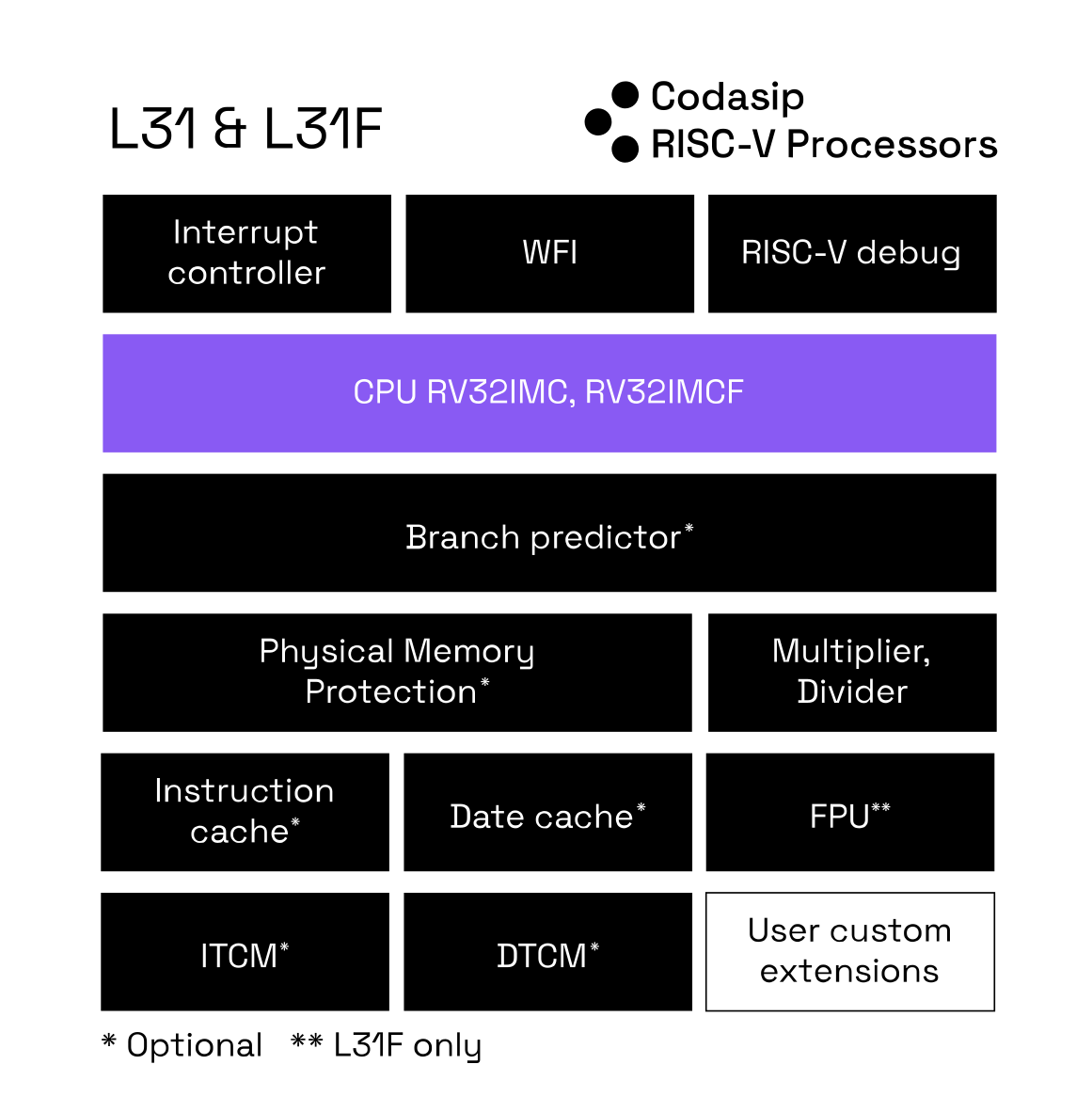

El punto de partida de la investigación es el núcleo Codasip L31 estándar, que se muestra a continuación con un bloque para extensiones personalizadas. En el documento técnico, Codasip describe la creación de cuatro instrucciones personalizadas para acelerar los filtros FIR y medianos: una que configura el flujo del filtro FIR, otra que configura el flujo del filtro mediano, una que configura los coeficientes FIR y otra que borra el FIFO.

Diagrama de bloques L31. Fuente: Codasip

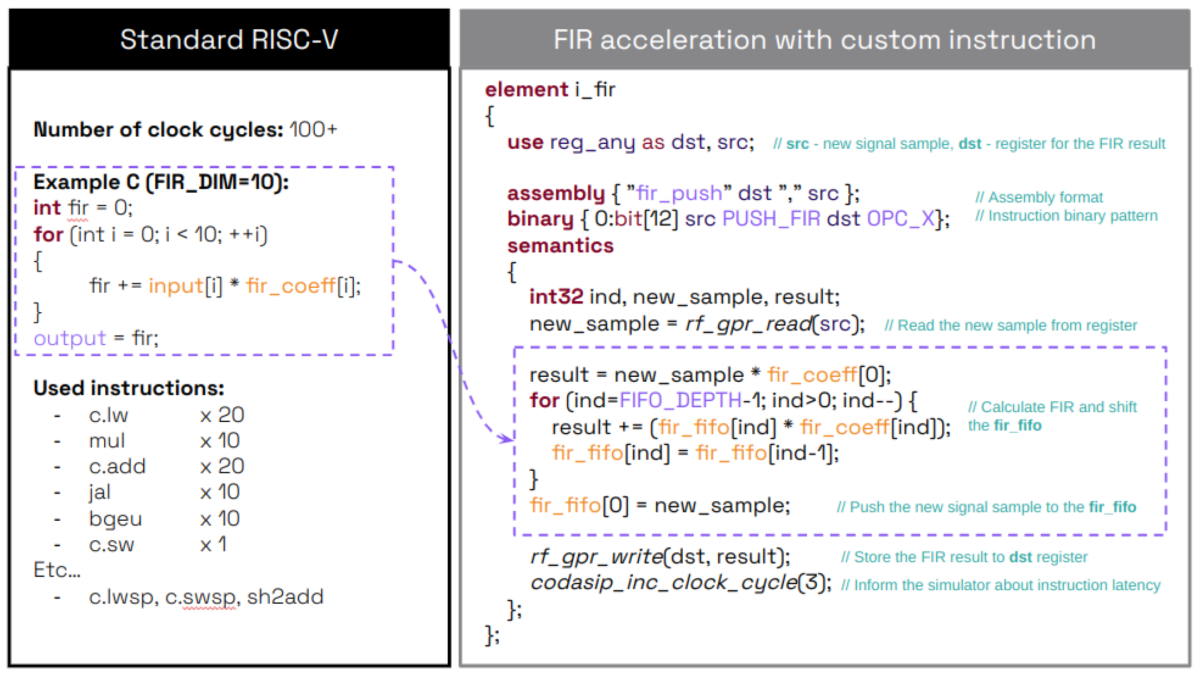

El lenguaje CodAL de Codasip simplifica la descripción de las características del procesador en una sintaxis compacta similar a C++. Codasip Studio convierte el marcado CodAL a RTL para que los diseñadores puedan trabajar en un lenguaje de alto nivel más familiar. La instrucción “fir_push” representada en CodAL es el más simple de los dos ejemplos; El documento técnico tiene una discusión completa sobre la instrucción más compleja “med_push” y la construcción de un modelo de máquina de estado con precisión de ciclo para ambas instrucciones.

Implementación de instrucciones personalizadas CodAL para el flujo de filtrado FIR. Fuente: Codasip

Al usar CodAL, el filtro FIR cabe en aproximadamente 150 líneas de código, y el filtro mediano es ligeramente más grande con aproximadamente 160 líneas, lo que describe por completo recursos de hardware e instrucciones de ciclo precisas listas para simular. En comparación, al usar Verilog, el filtro FIR es de 670 líneas de código y el filtro mediano es de 1180, sin el conocimiento automático del compilador ni del simulador.

Ampliación de RISC-V para ahorros sustanciales en PPA

La aceleración de los filtros FIR y medianos es solo una parte de una aplicación, pero los resultados muestran cómo es posible asumir rutinas cruciales ampliando la microarquitectura RISC-V. Guardaremos los detalles para el documento técnico: en resumen, en este enfoque se observa un aumento de rendimiento superior a 27 veces para el FIR o el filtro mediano, con solo un aumento del 37 % en el área central L31 para el FIR, menos para el el filtro mediano. Nuevamente, esto se puede lograr sin recurrir a RTL codificado a mano y sin tener que lidiar con extensiones de compilador y simulador: CodAL maneja esos detalles automáticamente.

Para conocer la historia completa, descargue el documento técnico de Codasip (acceso de registro para el texto completo):

Aceleradores de respuesta de impulso finito (FIR) y filtro mediano en CodAL

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Automoción / vehículos eléctricos, Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- ChartPrime. Eleve su juego comercial con ChartPrime. Accede Aquí.

- Desplazamientos de bloque. Modernización de la propiedad de compensaciones ambientales. Accede Aquí.

- Fuente: https://semiwiki.com/ip/codasip/334582-extending-risc-v-for-accelerating-fir-and-median-filters/