La reutilización del diseño ha permitido a los equipos de diseño de circuitos integrados crear diseños de mil millones de transistores en los que cientos de bloques de IP están preconstruidos a partir de fuentes internas o externas. Realizar un seguimiento de dónde proviene cada uno de estos bloques de IP, cuál es el estado de su versión, administrar la IP o incluso discernir el estado de su licencia puede ser un trabajo de tiempo completo si se realiza un seguimiento mediante métodos manuales. Otras grandes preguntas que deben responderse son dónde encontrar la IP adecuada o cómo hacer que otros sepan que ha creado una nueva IP que podría reutilizarse en nuevos proyectos.

Empresas como Cliosoft, ahora parte de AED de Keysight, llevan muchos años automatizando funciones para la reutilización de IP, como buscar IP, crear nueva IP y reutilizar IP de forma segura en sistemas. Está previsto un seminario web el 1 de noviembre a las 10:00 a. m. PT. Dominar el arte de gestionar la propiedad intelectual, los chiplets y los datos de diseño.

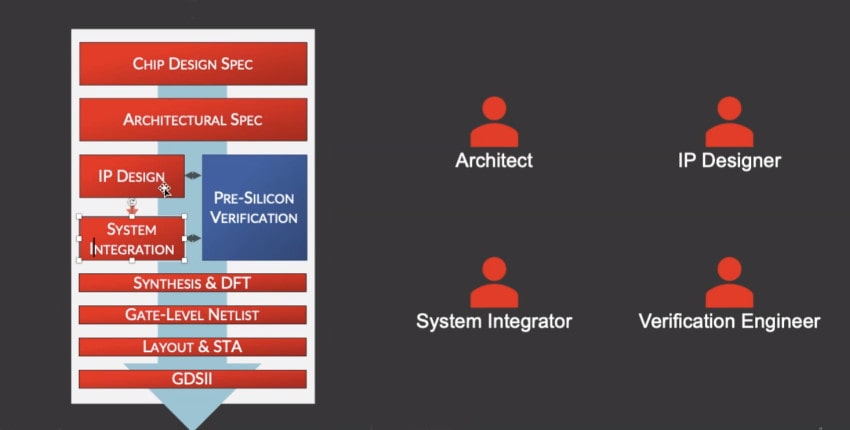

En el seminario web se revisará el flujo de diseño básico de SoC, junto con los múltiples roles de ingeniería que forman el equipo de diseño y verificación. Tener una forma para que cada uno de estos miembros del equipo se comunique y colabore durante la ideación e implementación del proyecto es crucial para el éxito.

Encontrar el bloque de IP correcto, ya sea internamente o de proveedores externos, se automatiza con Keysight Gestión de IP (HUB) herramienta. Los arquitectos de sistemas suelen dividir un diseño complejo en partes más pequeñas utilizando la jerarquía como abstracción y luego identifican todos los bloques de IP necesarios. Los miembros de los equipos de diseño y verificación pueden estar dispersos geográficamente, lo que genera desafíos de comunicación y documentación. Las herramientas adecuadas de gestión de datos ayudan con estas tareas de particionar un diseño electrónico, asegurar los bloques de IP necesarios e incluso geocercar la IP para cumplir con los acuerdos de licencia.

En el seminario web se abordan tanto el flujo de SoC como los flujos de diseño de Chiplet en términos de gestión de IP y datos de diseño. Los desafíos comunes para el diseño de sistemas incluyen la gestión de la lista de materiales, la resolución de conflictos de versiones de IP, el ensamblaje de subsistemas de IP, la conexión segura de bloques de IP a un NoC y la reutilización del conocimiento de diseño para conectarse a los NoC.

Un miembro del equipo puede actualizar el estado de un bloque de IP adjuntando una etiqueta a ese bloque, como Verificación lista, y luego informar automáticamente a otros miembros del equipo sobre el cambio de estado, para que todos conozcan el historial y la secuencia de quién ha trabajado en cada bloque de IP. y cuál es el siguiente paso en el flujo de diseño. Un ingeniero puede etiquetar un bloque de IP como aprobación RTL, luego un flujo de trabajo activa una instantánea o una versión de esa jerarquía utilizada para futuras auditorías y, finalmente, envía correos electrónicos a todas las partes interesadas. Industrias como el DOD y el sector aeroespacial tienen requisitos rigurosos sobre el seguimiento de las especificaciones y requisitos hasta su implementación, por lo que es necesario realizar auditorías para la trazabilidad.

Los equipos legales también están interesados en saber qué IP se incluye en cada diseño que se envía, para poder gestionar adecuadamente los acuerdos contractuales para los bloques de IP con licencia.

Las herramientas de Cliosoft están completamente integradas en el flujo de herramientas Keysight EDA, junto con los flujos de herramientas IC de Cadence y Synopsys. Los usuarios de la herramienta EDA permanecen dentro de la herramienta de su proveedor favorito para acceder a todas las funciones de gestión de datos (DM), lo que permite una curva de aprendizaje rápida. Herramientas de gestión de proyectos como Jira También están integrados, junto con herramientas de seguimiento de errores como Bugzilla.

Resumen

Asista al seminario web en 1 de noviembre a las 10:00 a. m. (hora del Pacífico) para obtener más información sobre la gestión de datos e IP, incluso la gestión del ciclo de vida de ingeniería desde la especificación del chip hasta la salida en cinta. Tanto los enfoques de diseño de SoC como de chiplets se benefician del uso de una automatización más allá de lo que puede proporcionar un sistema PLM típico.

Blogs relacionados

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/eda/336838-managing-ip-chiplets-and-design-data/