Las diferencias entre la creación de prototipos comerciales de FPGA ("Creación de prototipos") y la emulación han sido bien documentadas por los proveedores de soluciones comerciales de creación de prototipos y emulación, y los medios técnicos. Lo que ha recibido menos cobertura es cómo los beneficios de creación de prototipos difieren de los beneficios de emulación. Ambos están destinados a reducir el tiempo y los recursos necesarios para lograr una verificación completa de los sistemas electrónicos basados en chips; ambos se ejecutan mucho más rápido que la simulación de software para la verificación, en un contexto modelado del software de ejecución del producto final, con alta visibilidad del nodo de diseño interno. durante la operación.

Ambas son formas de simulación acelerada por hardware que se originaron, en parte, a partir del intento desesperado de Intel a mediados de la década de 1980 para hacer frente a los crecientes requisitos de recursos de ingeniería proyectados para la complejidad del diseño de chips de procesadores futuros. Ambos ofrecen su mayor valor cuando se utilizan para permitir el desarrollo conjunto temprano de hardware/software que cambia los cronogramas de desarrollo a la izquierda por meses en comparación con el desarrollo secuencial de hardware/software. De hecho, fue el riesgo de llegar tarde al mercado lo que motivó a muchos de los primeros desarrolladores de productos a invertir millones de dólares en Emulación para gestionar los riesgos del tiempo de comercialización. En ese momento, se propuso que un producto basado en chips con un esperado ingresos de por vida de decir $ 50 millones, y un producto momentos involvidables de digamos 3 años, sufriría $8M de pérdida de ingresos si la entrada al mercado se retrasara 2 meses, y se propuso una ecuación para modelar la pérdida de ingresos.

Figura 1: Pérdida de ingresos debido al retraso en el tiempo de comercialización

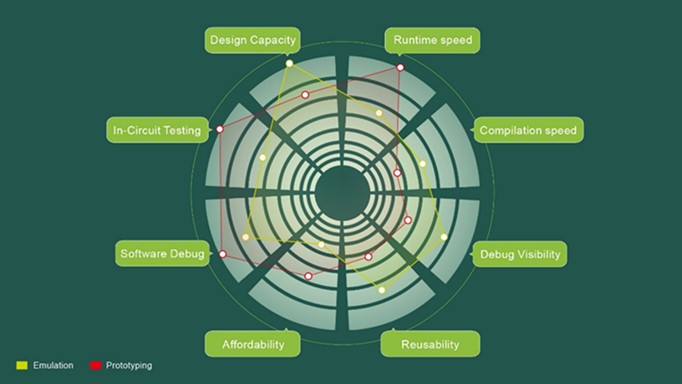

Diagrama de araña de creación de prototipos frente a emulación

Una forma de visualizar la diferencia entre la creación de prototipos y la emulación es con un "gráfico de araña" (llamado así por su parecido con una tela de araña). El gráfico de araña Prototipos vs. Emulación a continuación destaca las diferencias entre estos dos métodos de verificación, que pueden resumirse en velocidad de ejecución, Capacidad de diseñoy asequibilidad – todas las demás diferencias, a veces no insignificantes, son “artefactos” de estas tres diferencias fundamentales. Velocidad de compilación es una función de Capacidad de diseño – cuanto mayor sea el diseño, mayor será el tiempo de compilación. Se puede conectar cualquier plataforma de verificación en circuito a un sistema objetivo de hardware con los buffers de velocidad de interfaz apropiados, pero la verificación velocidad de ejecución está limitado por la plataforma de verificación – Emulación velocidad de ejecución es mucho más rápido que la simulación de software y se puede lograr la creación de prototipos velocidades de ejecución son mucho más altos que la emulación alcanzable velocidades de ejecución.

Asimismo, cualquier plataforma de verificación puede ser utilizada para depuración de software para los períodos de ejecución del software, y cuanto mayor sea velocidades de ejecución de creación de prototipos permiten períodos mucho más largos de ejecución de software, por lo tanto, son capaces de más completo depuración de software sesiones que suelen ser suficientes para el desarrollo de software anterior. Y visibilidad de depuración podría incluir cada nodo de diseño interno en un prototipo o un emulador, pero cada nodo de diseño depurar sonda requiere otra conexión de cable de interconexión interna en las implementaciones de emulación y creación de prototipos basadas en FPGA, lo que afecta Capacidad de diseño y velocidad de ejecución.

Finalmente, reutilización es una función de cuán única debe ser la plataforma de creación de prototipos o emulación para lograr la verificación deseada Capacidad de diseño, velocidad de ejecución, y objetivos de operación en circuito: cuanto más "a medida" sea la plataforma para cumplir con los requisitos de verificación específicos, menos reutilizables será la plataforma. El propio hardware subyacente de creación de prototipos o emulación es altamente reutilizables, pero las compilaciones de diseño, las adaptaciones internas de bloques de IP y las conexiones "externas" del sistema de destino tendrán una reutilización limitada para el próximo diseño y contexto de diseño, a menos que el próximo diseño sea una derivación cercana del diseño anterior donde gran parte de la plataforma de verificación no lo hace. No es necesario cambiar y se puede reutilizar.

Figura 2: Creación de prototipos de FPGA frente a emulación

Has recorrido un largo camino bebé

Los primeros emuladores comerciales (alrededor de la década de 1990) ni siquiera eran tan capaces como las soluciones comerciales de creación de prototipos de hoy en día, y lo que se conocía como "creación de prototipos" en esos días todavía era el dominio de los aventureros jinetes de FPGA "hágalo usted mismo". Los emuladores de hoy en día han evolucionado a soluciones "grandes" que parecen ser aceleradores de hardware de simulación de propósito especial, implementados con FPGA comerciales o silicio personalizado, que han cambiado el rendimiento por un mejor tiempo/esfuerzo de implementación. Los emuladores de hoy también vienen con metodologías restrictivas adaptadas a implementaciones de hardware de emulación específicas que permiten que la implementación del diseño sea más automática, más predecible, con alta visibilidad del nodo interno del diseño, y para esta automatización y una implementación más predecible, los usuarios están dispuestos a sacrificar "algo" velocidad de ejecución.

Los emuladores modernos tienden a centrarse en proporcionar una verificación altamente automatizada y versátil: soporte para múltiples lenguajes de programación, alta capacidad de modelo de diseño bajo prueba ("DUT") (equivalente a 1 mil millones de puertas y más), altos niveles de automatización de inicio (algunos semanas) que minimiza la intervención manual, soporte para múltiples modos de verificación como aceleración basada en transacciones ("TBA"), emulación en circuito ("ICE") y modo de emulador rápido ("QEMU"), dirigido a múltiples escenarios de uso para el sistema Verificación funcional a nivel de chips y diseños de IP y verificación de software integrado.

La creación de prototipos, por otro lado, es más asequible, y es capaz de mucho más rápido velocidades de ejecución que la emulación, por lo que la creación de prototipos puede ser una mejor opción que la emulación para ciertos entornos de verificación. Si se prefiere una "plataforma de verificación personal" (herramientas de diseño de escritorio, sitios de desarrollo dispersos geográficamente, etc.), el asequibilidad of Prototyping hace que sea práctico para cada desarrollador tener una plataforma de verificación personal. La creación de prototipos también permite a los desarrolladores enviar una plataforma de verificación a los clientes antes de la disponibilidad del silicio en desarrollo.

Los rápidos avances en la capacidad lógica de FPGA de paquete único (densidad de puerta utilizable) y el rendimiento han alentado a más desarrolladores de chips a considerar la creación de prototipos como una parte esencial de su estrategia de verificación, especialmente si todo el diseño se puede hacer para "encajar" en un solo FPGA. Los FPGA de vanguardia actuales (Xilinx Virtex UltraScale+ VU19P e Intel Stratix GX 10M) tienen capacidades lógicas utilizables de hasta aproximadamente 50 millones de puertas ASIC equivalentes por FPGA.

Figura 3: Intel Stratix GX 10M (10.2 millones de elementos lógicos) y FPGA Xilinx VU19P (3.8 millones de celdas lógicas del sistema)

Si todo el diseño a ser Prototipado se puede encajar en un solo FPGA, muchos de los desafíos de implementación de Prototipos, y la velocidad de ejecución Se pueden evitar las limitaciones de la interconexión entre FPGA. Una vez que el diseño se extiende a múltiples FPGA, el diseño se debe dividir en bloques para cada FPGA, se debe garantizar la temporización de múltiples FPGA y las señales entre FPGA se deben conectar con cables de alto rendimiento entre las FPGA. Desafortunadamente, el conteo de pines de E/S de los principales FPGA comerciales no ha aumentado tan rápido como las capacidades lógicas de los FPGA; 10 de miles de interconexiones bloque a bloque. Afortunadamente, los requisitos para una mayor interconexión entre FPGA no son insuperables para los proyectos de creación de prototipos debido a la disponibilidad de automatización de multiplexación de pines de vanguardia que se puede aplicar para crear pines de interconexión de E/S FPGA "virtuales", pero esta solución viene en un costo de menor velocidades de tiempo de ejecución.

Entonces, ¿cómo pueden beneficiarlo los prototipos y la emulación?

En resumen, la creación de prototipos de FPGA hoy en día es generalmente más asequible que la emulación, puede lograr mucho más alto velocidades de ejecucióny Capacidad de diseño se ha ampliado en gran medida gracias a la tecnología FPGA de vanguardia actual. La emulación, por otro lado, viene con un mayor costo de propiedad, una mayor automatización de la implementación y proporciona una verificación más similar a la simulación para la depuración del diseño. De hecho, si puede pagar tanto la creación de prototipos como la emulación, la depuración con creación de prototipos generalmente se limita a identificar y aislar problemas de hardware/software de diseño durante largos períodos de operación de diseño que luego se reproducen en Emulación para una depuración detallada. Se recomienda que sea claro desde el inicio del proyecto sobre sus objetivos de verificación (¿qué es suficiente para aprobar la aprobación, etc.?), sus prioridades de verificación (por ejemplo, velocidad de tiempo de ejecución frente a visibilidad del diseño frente a tiempo de implementación, etc.), el conjunto de habilidades de su equipo de diseño con respecto a obtener el mejor valor de las plataformas de creación de prototipos y/o emulación, un cálculo rápido del ROI para su inversión en herramientas de verificación, y luego presupuestar en consecuencia. Solo entonces debe proceder con la elección y el despliegue de prototipos y/o emulación de FPGA.

S2C puede ayudar

S2C es un proveedor global líder de soluciones de creación de prototipos de FPGA para los diseños innovadores de SoC y ASIC de la actualidad, que ahora ocupa la segunda mayor participación en el mercado mundial de creación de prototipos. S2C ha brindado con éxito soluciones rápidas de creación de prototipos de SoC desde 2003. Con más de 500 clientes, incluidas 6 de las 15 principales empresas de semiconductores del mundo, nuestro equipo de ingeniería de clase mundial y el equipo de ventas centrado en el cliente son expertos en abordar las necesidades de verificación de SoC y ASIC de nuestros clientes. . S2C tiene oficinas y representantes de ventas en EE. UU., Europa, China continental, Hong Kong, Corea y Japón. Visite el sitio web de S2C en s2ceda.com para más información.

Lea también

Una conexión más rápida del dispositivo de creación de prototipos bajo prueba

Destacado proveedor veterano de soluciones de creación de prototipos de FPGA en #59DAC

Software de creación de prototipos de FPGA múltiple: nunca lo suficiente de algo bueno

Comparte esta publicación a través de:

- Coinsmart. El mejor intercambio de Bitcoin y criptografía de Europa.Haga clic aquí

- Platoblockchain. Inteligencia del Metaverso Web3. Conocimiento amplificado. Accede Aquí.

- Fuente: https://semiwiki.com/prototyping/s2c-eda/320852-ask-not-how-fpga-prototyping-differs-from-emulation-ask-how-fpga-prototyping-and-emulation-can-benefit-you/