Los arquitectos de sistemas tienen la difícil tarea de elegir la arquitectura más eficiente mediante la exploración de enfoques alternativos, al tiempo que rastrean y prueban los requisitos. Se recomienda utilizar un enfoque de ingeniería de sistemas basada en modelos (MBSE) para lograr estos objetivos, antes de quedar atrapado en detalles de implementación de bajo nivel como el código RTL. Mirabilis es un proveedor de EDA en DAC este año que tiene como objetivo utilizar una metodología MBSE a través de su herramienta VisualSim. Hablé con Deepak Shankar, fundador de Diseño Mirabilis por teléfono esta semana para obtener una vista previa de lo que están haciendo en DAC.

Los tres grandes mensajes de Mirabilis este año para DAC que interesarán a los arquitectos de sistemas son:

1. Integración con Ingeniería de Sistemas Basada en Modelos

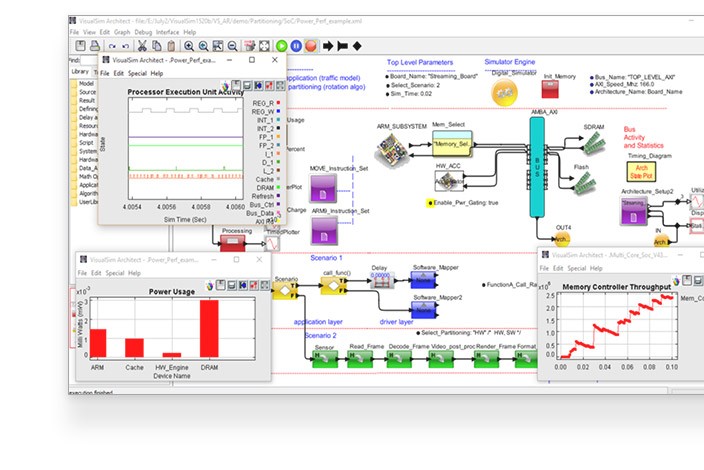

Los arquitectos pueden importar sus modelos SysML existentes a la herramienta VisualSim. La adopción de SysML comenzó en la comunidad de defensa y ahora incluso las empresas de semiconductores a nivel de sistema lo están utilizando. SysML puede administrar su código, pero no puede predecir cuál será el rendimiento y la potencia cuando se mapee a HW como un SoC. SysML no puede determinar la contención de caché, porque no hay comprensión de la latencia. El uso de VisualSim con MBSE proporciona los datos de requisitos, lo que le permite medir la latencia, ver la ocupación del búfer e incluso realizar un seguimiento de los requisitos de radiación.

2. Adición del entorno de modelado RISC-V

RISC-V es una arquitectura de conjunto de instrucciones (ISA) muy popular que se puede ampliar para dominios específicos, pero ¿cómo haría comparaciones de potencia y rendimiento entre el uso de SiFive o una arquitectura ARM? ¿Qué hay de los puntos de referencia a nivel del sistema?

Con Mirabilis hay modelos prediseñados de RISC-V IP, además, puede incluso crear su propia arquitectura RISC-V especial. Para Network On Chip (NoC), puede elegir entre modelos para Arteris NoC o ARM NoC. En VisualSim Architect, puede ejecutar puntos de referencia para RISC-V y ver qué sucedería si sus datos se almacenan en caché o si tiene que usar RAM externa. También puede ver el rendimiento e identificar los cuellos de botella de su arquitectura. Este análisis le permite evaluar núcleos RISC-V para usar dentro de un SoC, o modelar un SoC para entregar a los clientes para que puedan comenzar a planificar la arquitectura de sus productos finales. VisualSim le permite a un ingeniero comprender las tuberías y todo el sistema en una sola plataforma.

3. Creó un nuevo mecanismo de empaque

Un proveedor central de RISC-V podría empaquetar su modelo de alto nivel incluso antes de que comience el desarrollo del producto, para usarlo dentro de un SoC y luego entregárselo a su cliente final para ver cómo funciona el sistema completo. Un proveedor de semiconductores, un proveedor de nivel 1 y un cliente pueden compartir los mismos modelos ejecutables. Denso es un ejemplo de modelos de uso compartido de clientes de sus ECU para automóviles como proveedor de nivel 1 para empresas automotrices, y ahorraron un 40 % del tiempo de desarrollo mediante el uso de VisualSim.

Papel DAC

Mirabilis tiene un documento DAC sobre modelado de sistemas y análisis de fallas en aviónica, junto con una aplicación de defensa de EE. UU.

Asista a esta presentación el martes 11 de julio, de 2:24 p. m. a 2:42 p. m. PDT, salón 2008 en el Nivel 2, como parte de la pista de Software y sistemas integrados.

Stand DAC

Encontrará a Mirabilis en el stand n.° 2217, que está en el segundo piso de Moscone West, y en su stand habrá tres técnicos con quienes hablar. Mientras que otros proveedores tienden a mostrar solo diapositivas de PowerPoint, en su lugar verá una demostración en vivo de la herramienta VisualSim Architect en acción, ahora eso es confianza.

También puede registrarse para una discusión privada en sus suites solicitando en línea aquí.

Resumen

El diseño del sistema y el modelado del sistema se han vuelto mucho más fáciles, precisos y, al usar IP a nivel de sistema, los arquitectos de su sistema analizarán rápidamente y explorarán más a fondo que con otros métodos. En este nivel de abstracción, su equipo puede analizar y descubrir cuellos de botella arquitectónicos antes de que comience la implementación detallada de RTL.

Disfrute de un poco de chocolate en el puesto, he oído que es bastante sabroso.

Blogs relacionados

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Automoción / vehículos eléctricos, Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- Desplazamientos de bloque. Modernización de la propiedad de compensaciones ambientales. Accede Aquí.

- Fuente: https://semiwiki.com/ip/331578-mirabilis-invites-system-architects-at-dac-2023-in-san-francisco/