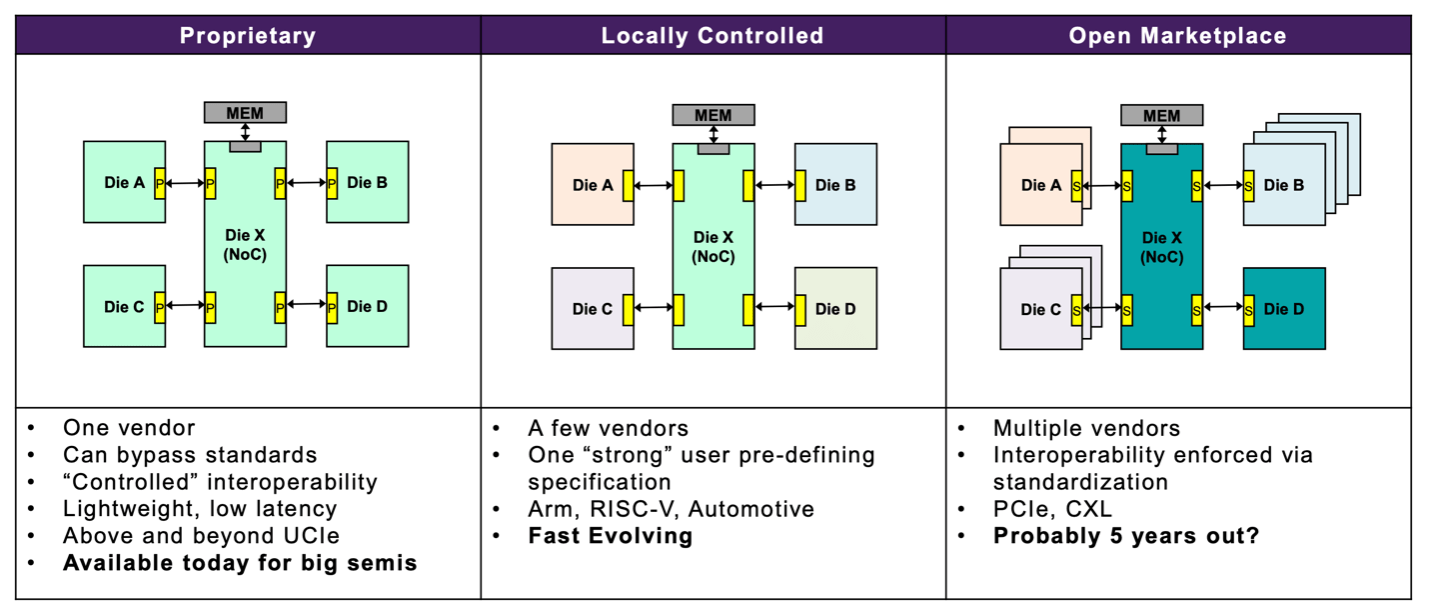

Recientemente hablé con Frank Schirrmeister (Soluciones y Desarrollo Comercial, Arteris) sobre el estado de progreso hacia el ideal de chiplet abierto. Ya sabe, dónde se puede ensamblar un sistema de múltiples matrices en paquete con conexiones UCIe (u otras) que conectan perfectamente los flujos de datos entre matrices. Si la inteligencia artificial general y la computación cuántica a escala industrial están a la vuelta de la esquina, ¿seguramente cualquier problema restante en el diseño de chiplets abiertos debería ser fácil de resolver? Según Frank, la respuesta es sí y no. Para un par de grupos privilegiados todo es posible y hoy se está poniendo en práctica. Para los mercados abiertos más grandes, no tanto, al menos no en el corto plazo.

Cortesía arterisa

Sistemas de matrices múltiples y soluciones patentadas

Los sistemas de matrices múltiples abordan la demanda interminable de construir sistemas más grandes y complejos (para el procesamiento LLM, por ejemplo) cuando están limitados por una serie de limitaciones de semiconductores: solo se puede colocar tanta lógica en una matriz; algunas funciones como analógica y DRAM funcionan mejor en procesos que no son óptimos para la lógica; e incluso si de alguna manera se pudiera colocar más en un solo dado, el rendimiento se desplomaría y los costos se dispararían.

Durante el último año, Intel, AMD y Nvidia lanzaron productos de procesador basados en arquitecturas de chiplet. Lo que es exclusivo de estos productos en este contexto es que cada una de estas empresas construyó sus propios chiplets, junto con la infraestructura y la conectividad que los ensamblan en un sistema completo de múltiples matrices. No dependen de proveedores de chiplets externos ni de proveedores de IP de comunicación de chiplet a chiplet externos. Al controlar todo internamente y guiar a sus proveedores en consecuencia, pueden ajustar y validar los sistemas que construyeron internamente comparándolos con sus propios y extensos conjuntos de pruebas. Algunas otras empresas muy grandes integradas verticalmente también pueden pertenecer a esta clase. Me han dicho que Meta puede ser ahora uno de estos, y me sorprendería que Apple no estuviera también manejando todo su propio diseño de matrices múltiples.

Para cualquiera que quiera construir un sistema de múltiples troqueles, todo esto es interesante, pero sigue siendo una prueba de concepto. Funciona muy bien para Intel, AMD y Nvidia, pero se necesita más para los creadores de sistemas que no tienen ese nivel de control. Si bien la UCIe (entre otras opciones) debería, en principio, encargarse de la comunicación de muerte a muerte, la realidad sugiere que el desafío aún no está superado.

Por cierto, también existe una tendencia paralela; Las placas de circuito impreso (PCB) son cada vez más pequeñas. Aquí la industria ha visto muchos tipos diferentes de enfoques de empaque, y los usuarios están acostumbrados a integrar múltiples troqueles en sustratos para diseños que no desafían el límite de retícula mencionado anteriormente. Ambas tendencias convergen en los chiplets, aunque con diferentes enfoques metodológicos de diseño: PCB miniaturizados frente a piezas desnudas de silicio codiseñadas o interoperables.

Chiplets abiertos e interfaces de comunicaciones interoperables

En teoría, el uso de estándares como UCIe para la comunicación entre matrices debería resolver los problemas de comunicación entre matrices, algo esencial para permitir un verdadero ecosistema de chiplets abierto. Si esto funciona como se anuncia, entonces los chiplets deberían poder comunicarse incluso si provienen de diferentes proveedores de chipsets, están construidos en diferentes fundiciones, etc. Desafortunadamente, el cumplimiento del estándar está demostrando ser una condición necesaria pero insuficiente para garantizar la interoperabilidad entre dos lados de la red. (digamos) un enlace UCIe. Si bien los PHY se pueden verificar mediante diagramas oculares, todavía existe variabilidad en las formas de empaquetar datos de protocolos como AXI y CHI a interfaces de transmisión como CXS y de allí a FDI, la interfaz de transmisión de UCIe.

Esto no es una revelación. En el mundo de las PC, las comunicaciones por cable e inalámbricas y otros dominios, el cumplimiento de los estándares es el paso 1. Los Plugfests para demostrar la interoperabilidad entre proveedores en el mundo real son el siguiente paso. Para las comunicaciones celulares, los operadores de redes requieren pruebas detalladas de interoperabilidad según sus requisitos. Parece que se necesita una infraestructura similar para las comunicaciones de chiplets, aunque eso puede ser un poco más desafiante porque no se puede conectar un conector a un chiplet. Frank me dice que ha oído que se están preparando planes, pero que no se espera que se generalicen en el corto plazo (PCie también tardó un tiempo). La industria ha anunciado casos tempranos de interoperabilidad UCIe, por ejemplo, entre Intel y Synopsys.

Una clase de constructores de sistemas tiene una respuesta sencilla a este problema. Son lo suficientemente poderosos como para obligar a sus proveedores a cumplir con el cumplimiento de su diseño. Si algo no funciona en sus casos de uso, las partes potencialmente culpables investigan y deben encontrar una solución. Algunos grandes fabricantes de equipos originales de automóviles pertenecen a esta clase, también algunas grandes empresas de HPC. Es probable que los problemas encontrados aquí sean pequeñas diferencias en las expectativas de márgenes, almacenamiento en búfer y otros parámetros que el estándar no define completamente. O simplemente errores no cubiertos en las pruebas de casos de uso de proveedores de chiplets/IP. Cualquiera que sea el problema, los proveedores deben solucionarlo. Es bueno ser el rey cuando se quiere crear un diseño basado en chiplets.

Para todos los demás

Llegar a la interoperabilidad hoy depende de dónde se ubica cada una de sus conexiones entre matrices en la gran matriz en constante evolución de pares de comunicación probados/cubiertos, considerando fuentes IP/PHY, diferencias de especificaciones y diferencias de casos de uso (enlaces coherentes versus no coherentes). . Los pares simétricos (todo igual en ambos lados) deberían (?) estar bien, pero los pares asimétricos son una apuesta a menos que se demuestren en producción. Según Frank, este desafío es especialmente visible desde el mundo de NoC. Dice que los clientes preguntan si el Arteris NoC funciona con una IP de controlador UCIe particular. Pregunta razonable que pensarías.

Pero el NoC habla con un protocolo para transmitir convertidor, que luego habla con un PHY. Eso se comunica a través de un enlace a un PHY en el segundo chiplet, luego a un convertidor de flujo a protocolo y luego al NoC en ese chiplet. Todo el mundo cumple plenamente con el estándar, pero aún así el enlace no funciona, a menos que se haya demostrado que funciona en producción. Pruebas de interoperabilidad mucho más estrictas eventualmente resolverán este problema, pero eso puede tardar dentro de cinco años. Mientras tanto, arterisa y los clientes están completando celdas en la matriz de interoperabilidad una (o tal vez algunas) a la vez.

En pocas palabras, los chiplets son reales, totalmente bajo control para el constructor de sistemas integrados verticalmente, evolucionan rápidamente bajo clientes autocráticos y avanzan poco a poco para todos los demás. Puedes leer más AQUÍ.

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/chiplet/341582-moderating-our-open-chiplet-enthusiasm-a-noc-perspective/