En la era de la rápida innovación tecnológica, los centros de datos a hiperescala están evolucionando a un ritmo vertiginoso. Con los continuos avances en CPU, GPU, aceleradores y conmutadores, las transferencias de datos más rápidas ahora son primordiales. A la vanguardia de este avance está PCI Express (PCIe®), que se ha convertido en el estándar de interconexión de facto para transferencias de datos de alta velocidad entre nodos de procesamiento y computación.

Duplicar las velocidades de datos: la tendencia continúa

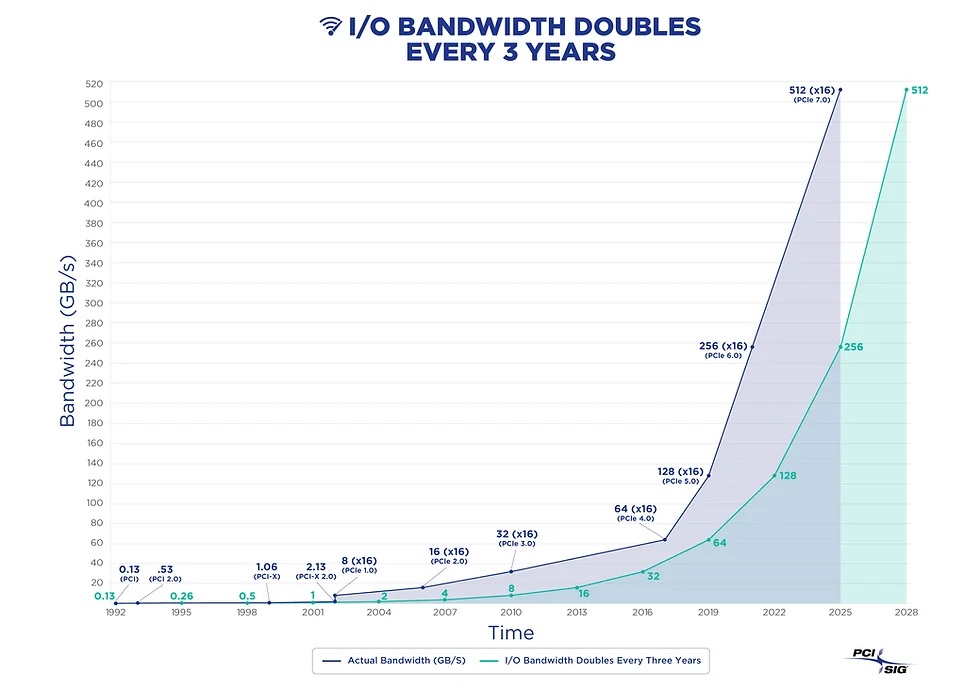

El consorcio PCI-SIG®, responsable de la interfaz PCIe, tiene un historial de lanzar una nueva generación de PCIe aproximadamente cada tres años. Esto invariablemente ha duplicado la tasa de datos durante la última década. La última versión de PCI-SIG, PCIe 6.0.1, marca el comienzo de la señalización de modulación de amplitud de pulso (PAM4) multinivel, con una asombrosa velocidad de transferencia de 64 GT/s en una dirección en un solo carril. En particular, durante la PCI-SIG DevCon 2022, se anunció la especificación PCIe 7.0, que duplica la velocidad de datos a 128 GT/s, enfatizando tanto la eficiencia energética como un mayor ancho de banda.

Figura 1. El ancho de banda de E/S PCI-SIG se duplica cada 3 años. Desde PCI-SIG

Pruebas estrictas de cumplimiento e interoperabilidad

Es importante comprender que más allá de los centros de datos a hiperescala, la implementación de la tecnología PCIe en campos como dispositivos portátiles, servidores, automoción, aplicaciones industriales y más exige una alta confiabilidad y rentabilidad. Esto requiere pruebas de cumplimiento rigurosas de los productos para garantizar que se alineen con la especificación PCIe 6.0.1 y puedan interoperar exitosamente con otros dispositivos PCIe.

Revelando la señalización PAM4 y sus implicaciones

La integración de la señalización PAM4 en PCIe 6.0.1 es clave. A diferencia de la señalización sin retorno a cero (NRZ), que utilizaba dos niveles de señal distintos, PAM4 utiliza cuatro y transmite dos bits de información dentro de un único intervalo de unidad (UI). Esta modificación introduce nuevos desafíos como interferencias cruzadas, reflejos de señal y ruido en la fuente de alimentación. La especificación PCIe 6.0.1 ha introducido la relación de distorsión señal-ruido (SNDR) para abordar estos desafíos, encapsulando tanto el ruido tradicional como los deterioros no compensables dentro de la señal eléctrica. La clave es comprender los problemas de integridad de la señal en los canales de comunicación de alta velocidad debido a la diafonía y las pérdidas por reflexión con el análisis de la frecuencia y el dominio del tiempo. Se utilizan técnicas de medición de canales y varias técnicas de mejora de señal con ecualización de transmisor y receptor PCIe 6.0 para compensar las características no ideales del canal.

Resumen

Los avances en la tecnología PCIe han allanado el camino para una nueva era de capacidades de transferencia de datos, con PCIe 6.0.1 y el próximo PCIe 7.0 estableciendo nuevos puntos de referencia. Sin embargo, mayores capacidades conllevan mayores desafíos, particularmente para garantizar el cumplimiento y la interoperabilidad. Asociaciones como Synopsys y Tektronix están liderando la tarea de abordar estos desafíos, garantizando que la tecnología no solo cumpla sino supere las demandas de la era digital actual.

¡Únase a nuestro seminario web!

¿Quiere profundizar en las simulaciones de PCIe y las pruebas eléctricas? Únase a nuestro próximo seminario web el martes 10 de octubre, de 9:00 a. m. a 10:00 a. m. PDT, donde los expertos de la industria de Synopsys y Tektronix discutirán lo último en tecnología PCIe y la importancia de metodologías de prueba sólidas. ¡Haga clic aquí para registrarse ahora!

Ponentes:

David Bouse es líder tecnológico principal en Tektronix y colaborador activo de PCI-SIG con experiencia en SERDES de alta velocidad, incluidas metodologías de prueba de transmisores y receptores, algoritmos DSP para señalización NRZ/PAM4, caracterización de reloj y arquitectura de software de automatización.

Madhumita Sanyal es gerente técnica de personal senior de la cartera de SerDes de alta velocidad de Synopsys. Tiene +17 años de experiencia en diseño y aplicación de productos ASIC WLAN, bibliotecas lógicas, memorias integradas e IP de señal mixta.

Sobre Synopsys

Synopsys, Inc. (Nasdaq: SNPS) es el socio de Silicon to Software ™ para empresas innovadoras que desarrollan productos electrónicos y aplicaciones de software en las que confiamos todos los días. Como empresa S&P 500, Synopsys tiene una larga trayectoria como líder mundial en automatización de diseño electrónico (EDA) e IP de semiconductores y ofrece la cartera más amplia de la industria de herramientas y servicios de prueba de seguridad de aplicaciones. Ya sea que sea un diseñador de sistema en chip (SoC) que crea semiconductores avanzados o un desarrollador de software que escribe código más seguro y de alta calidad, Synopsys tiene las soluciones necesarias para ofrecer productos innovadores. Obtenga más información en www.sinopsis.com.

Lea también

Motor de IA de próxima generación para aplicaciones de visión inteligente

Pruebas QED habilitadas formalmente para VC en un núcleo RISC-V

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Automoción / vehículos eléctricos, Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- ChartPrime. Eleve su juego comercial con ChartPrime. Accede Aquí.

- Desplazamientos de bloque. Modernización de la propiedad de compensaciones ambientales. Accede Aquí.

- Fuente: https://semiwiki.com/events/333825-why-rigorous-testing-is-so-important-for-pci-express-6-0/