Durante décadas, una forma de jerarquía estructural ha sido el principal medio para manejar la complejidad en el diseño de chips. No siempre es perfecto y no existe una forma ideal de dividir y conquistar porque eso necesitaría centrarse en el análisis que se realiza. De hecho, la mayoría de los sistemas pueden verse desde una variedad de jerarquías diferentes, igualmente correctas y juntas formando una heterarquía.

La forma más sencilla de pensar en la forma de jerarquía que se utiliza hoy en día es pedirle a un ingeniero que diseñe conceptualmente un sistema. Probablemente comenzarán a dibujar un diagrama de bloques que contenga bloques grandes con etiquetas como CPU, codificador, subsistema de visualización, etc. Esta no es una jerarquía funcional, aunque se considera que muchos de los bloques divididos proporcionan una función. Tampoco se trata de una pura descomposición estructural, porque dentro de un chip todo se convierte en un mar amorfo de transistores.

Ese diagrama sigue aproximadamente las jerarquías desarrolladas para el diseño de placas de circuito impreso, que era una jerarquía de pines. En el nivel más bajo probablemente utilizó una biblioteca lógica, como la serie Texas Instruments 7400. Esos dispositivos tenían mapas de pines. El siguiente nivel de jerarquía era el nivel de la placa y los pines que se conectaban al backplane. Rara vez había una jerarquía intermedia, y los esquemas simplemente estaban distribuidos en varias "hojas". Más tarde, cuando los sistemas se volvieron más complejos, también se apoyaron las jerarquías estructurales.

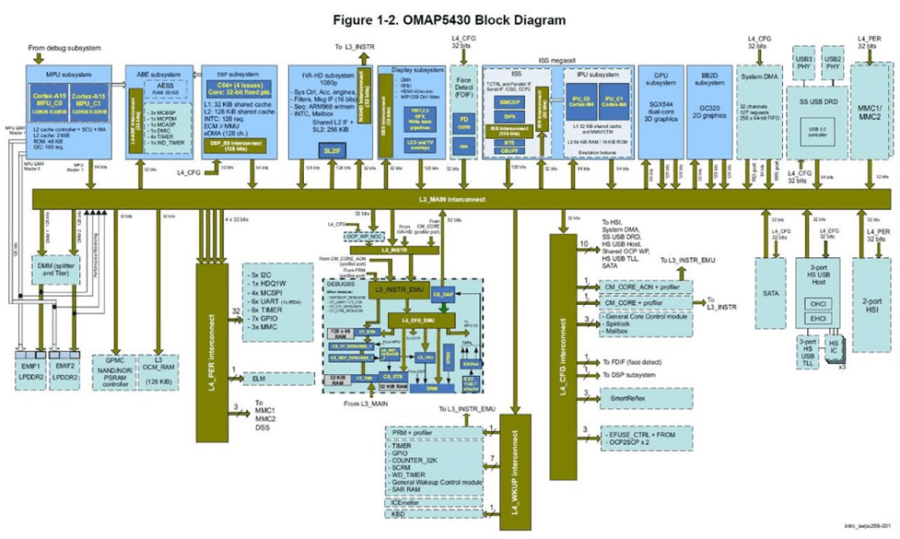

Fig. 1: Un diagrama de bloques típico para un chip complejo, alrededor de 2013. Fuente: Texas Instruments

Esta forma de jerarquía proporciona una encapsulación que permite que el desarrollo de cada uno de los bloques quede algo aislado y se minimicen las interdependencias. El nivel superior se convierte en el medio por el cual esos bloques se interconectan. Cada uno de los bloques divididos puede pasar entonces por una descomposición similar.

Hay varias razones por las que se utilizan jerarquías. "La capacidad es una", dice Marc Swinnen, director de marketing de productos de Ansys. “El problema se vuelve demasiado grande y hay que dividirlo en pedazos. Otra es la ingeniería concurrente. Tienes varios equipos que quieren trabajar en el diseño al mismo tiempo, por lo que los divides y trabajas en las piezas por separado. En tercer lugar está la reutilización. Quieres reutilizar bloques que otros han diseñado. Una forma sutil de esto es la biblioteca de celdas estándar, que en sí misma es una forma de jerarquía. La cuarta razón es la manejabilidad del volumen de datos. Una quinta razón son las estructuras repetitivas, como recuerdos, núcleos múltiples, donde simplemente se puede reutilizar de forma natural. Una sexta razón es el dominio mixto, como analógico/digital, donde hay diferentes estilos de diseño en cada bloque. Utilizarás diferentes herramientas y, por lo tanto, las dividirás jerárquicamente”.

Capacidad

A medida que los diseños crecen, muchos algoritmos tardan cada vez más en ejecutarse. Desglosarlos puede dar como resultado tiempos de ejecución más rápidos y requerir menos recursos. "Para diseños grandes, cuando se realiza la implementación física, pueden pasar días o incluso semanas hasta que estos diseños muy grandes terminen", dice Jim Schultz, gerente senior de productos de la Sinopsis grupo de implementación digital. “Si se estropea algo, los costos pueden ser significativos. La jerarquía es una forma de dividir y conquistar. Nos permite saber que podemos cerrar una sección del diseño a la vez. A medida que seguimos agregando funcionalidad y los chips se hacen cada vez más grandes, no se trata solo de tiempo de ejecución, sino también de quedarse sin recursos: la cantidad de memoria que se necesita para colocar todas estas instancias reutilizables excede la capacidad”.

Para poder realizar un análisis jerárquico, debe asegurarse de que las condiciones de contorno estén establecidas correctamente para cada bloque. Luego, es necesario realizar un análisis a través del límite en el nivel superior.

"El análisis plano lleva mucho tiempo pero proporciona total precisión", afirma Rimpy Chugh, director de producto de personal de Synopsys. “Adoptar un enfoque de caja negra en toda la jerarquía te da más velocidad, pero estás perdiendo precisión. Esto requiere una solución especializada (consulte la figura 2) donde la lógica de la interfaz de un bloque pueda conservarse para que pueda obtener el beneficio de velocidad y precisión al mismo tiempo. Es posible generar un modelo abstracto a nivel de IP y luego usarlo a nivel de SoC”.

Fig. 2: Flujo jerárquico utilizando modelos abstractos. Fuente: Sinopsis

Ingeniería concurrente

Los equipos de diseño ya no se limitan a un solo edificio. "Muchos diseños se están dividiendo para que un equipo trabaje en una jerarquía y otro equipo trabaje en otra jerarquía, y podrían estar en el mismo edificio o podrían estar repartidos por todo el mundo", dice Simon Rance, director de gestión de productos para la gestión de datos e IP en AED de Keysight. “Esto puede crear desafíos porque los equipos ahora trabajan a ritmos diferentes. Es importante tener una jerarquía estable porque es difícil realizar cambios más adelante. Por lo general, esto sucede solo como último recurso, pero en lugar de eso vemos equipos pegando o manipulando para que funcione. Puede ser feo, pero estamos viendo más de este desafío con los chiplets”.

Reutilizar

La jerarquía debe ser útil tanto de arriba hacia abajo como de abajo hacia arriba. "En el cuerpo humano, las células especializadas se organizan en sistemas y órganos que forman los componentes básicos que forman una persona", dice Brian LaBorde, director senior de marketing de productos de Cadencia. “De manera similar, los grupos de transistores forman circuitos o puertas lógicas que forman macros que se ensamblan en un sistema. En las últimas décadas hemos visto circuitos integrados cada vez más grandes con muchos circuitos especializados diferentes, todos integrados en un solo chip. La partición de estos diseños es virtual y está representada por jerarquía en una base de datos de diseños”.

Gestión de datos

Todos los diseños crean una gran cantidad de datos y hay que gestionarlos. "Con la gestión del ciclo de vida de la ingeniería y la necesidad de cumplir con los estándares de seguridad funcional, ya sea ISO 26262 para automoción o el estándar MIL882 para el sector aeroespacial militar, usted tiene muchos activos, desde documentos hasta verificación, criterios de prueba, planes de prueba de verificación y resultados", dice Keysight. Rance. “Todo eso debe conservarse en la jerarquía para que haya una trazabilidad total. De todos modos, rastrear todo en una jerarquía es difícil, pero también tienes todo fuera del diseño, como los planes de verificación y prueba. Cuando algo falla en la prueba, o peor aún, en el campo, regresa y descubre qué podría haber fallado. Si no tienes todos esos datos y metadatos adjuntos a la jerarquía, nunca los encontrarás”.

Estructuras repetitivas

Muchos diseños contienen estructuras repetitivas, ya sean celdas de memoria, pequeños conjuntos de procesadores o interfaces. Pero hay peligros ocultos en estos conjuntos. "Digamos que tiene 16 núcleos de CPU dispuestos en una cuadrícula de 4X4", dice Swinnen de Ansys. “En principio, todos son iguales, pero en realidad tienen diferentes condiciones límite. El entorno alrededor de los que están en el borde es diferente para cada uno. Si desea realizar una optimización, debe unificar cada uno, porque todos tienen parásitos únicos en los bordes. Siempre existe esta compensación. ¿Cómo se preserva la reutilización y, aun así, se encuentran los que son únicos? Se pone peor cuando miras cosas como las térmicas”.

Múltiples dominios

Si bien lo analógico y lo digital son muy diferentes, hay otros aspectos del flujo de desarrollo que también utilizan la separación de herramientas. "La idea general de EDA es tomar este problema complejo, simplificarlo y convertirlo en un problema estructural, dividirlo y simplificarlo realmente", dice Ron Press, director de habilitación tecnológica de Software de Siemens Digital Industries. “Eso es lo que hace el escaneo para DFT. Antes, incluso si tenían núcleos separados, intentaban hacer todo en una gran imagen plana. Luego tienes que esperar hasta más adelante en el diseño y tienes un problema mucho mayor. Ahora, con equipos de diseño distribuidos y núcleos que se reutilizan, la gente necesita la mayor cantidad de plug-and-play posible. Terminarán su diseño para el DFT, harán sus patrones para ese núcleo y luego eso se conectará en el nivel superior. Siempre que tenga algún tipo de aislamiento, como cadenas envolventes, pueden trabajar en esa pieza por separado, terminar el diseño DFT y terminar sus patrones. Eso hace que estos equipos sean independientes y hace que todo el proceso sea mucho más fácil”.

Problemas con la jerarquía estructural

Ningún sistema es perfecto y esta forma de jerarquía crea algunos problemas. "Definitivamente hay una sobrecarga relacionada con el diseño de restricciones en esos límites", dice Schultz de Synopsys. “Hay que romper las restricciones y definirlas correctamente, y llevarlas hasta los límites del bloque. Asegurarse de haber definido esos límites correctamente es un gran problema. El otro inconveniente es que, por diseño, cuando físicamente rompes algo en pedazos y dices que estas son mis particiones, cuando voy a implementarlo físicamente, no voy a optimizar más allá de ese límite. No se puede optimizar: ese límite ahora está fijo. Si es necesario realizar una optimización en esa jerarquía, no puede realizarla. Tú mismo estás limitado”.

Esto puede afectar a varias herramientas y flujos. "Si hacen un plan de nivel superior con DFT jerárquico, podrían planear que muchos pines vayan a un núcleo", dice Press de Siemens. “Entonces resulta que el núcleo no necesita demasiados patrones, y este otro núcleo al que asignaron una cantidad similar de pines necesita muchos más patrones. Si han congelado su diseño desde el principio, desde el nivel superior, entonces su entrega de patrones no será tan eficiente”.

Establecer una jerarquía incorrecta puede limitarte de múltiples maneras. "Uno de los grandes problemas, especialmente con los SoC grandes, es que las redes y las comunicaciones pueden crear congestión", añade Schultz. “Vemos congestión en todo el chip, especialmente cuando el diseño ha sido mal dividido. Veo bloques que hablan a través de otros bloques y hay que crear canales de comunicación. Eso puede causar mucha congestión en el diseño. Además, es mucho más difícil cumplir con los requisitos de tiempo cuando haces algo así, porque no puedes optimizar fácilmente esa ruta completa. Tienes que optimizar cada bloque individualmente y esperar que todos los caminos funcionen”.

Pueden producirse cambios sutiles en los límites. "Cuando lindas con dos bloques, tienes una conexión lógica entre ellos, pero no hay nada físicamente allí", dice Swinnen. “Los pines simplemente se tocan pero no hay ningún cable. Pero en tu lista de redes tienes un cable que se supone que debe estar ahí. Se supone que tiene una resistencia, una capacitancia. Tienes un cable lógico pero no un cable físico. Luego están los conductos de alimentación, donde los cables entran por un lado de un bloque, pasan a través del bloque y salen por el otro extremo. Hay pines, hay cables físicos, pero no hay cables lógicos. Lógicamente no existe. No dibujas eso en tus esquemas”.

Algunas herramientas pueden solucionar jerarquías deficientes, pero solucionarlas crea otros problemas. "Tienes una jerarquía lógica cuando desarrollas el RTL y lo sintetizas", dice Schultz. “Cuando haces tu diseño físico, esas jerarquías lógicas tienen que asignarse uno a uno a una partición física. Lo que termina sucediendo es que, en mi jerarquía lógica, puedo tener un hijo que está hablando con el niño debajo de esa jerarquía lógica que realmente está hablando mucho con algo que está bajo otro padre, y esos dos padres se convierten en sus propias particiones físicas. Esos dos padres pueden ubicarse físicamente en lados opuestos del chip. La jerarquía lógica no favorece la implementación física. La forma de gestionar esto es mediante la reestructuración de RTL. Ahora estamos empezando a mover cosas y reparar la lógica, pero eso no es algo que un diseñador lógico o RTL puro vaya a saber. Esa información sólo surge cuando se tiene en cuenta la jerarquía física. Es necesario que haya una comunicación entre los dos para poder optimizar realmente esa jerarquía física”.

Esto sucede en otros lugares del flujo. "Un NoC se ubica en el nivel superior de la cabina, donde se tienen los aspectos de integración de toda la jerarquía", dice Frank Schirrmeister, vicepresidente de soluciones y desarrollo comercial de arterisa. “Cuando se necesitan cambios en la jerarquía, tal vez debido a dos propiedades no funcionales diferentes entre dominios de poder, refactorizar el RTL puede ser sencillo. Tener un mayor nivel de integración para la jerarquía le ayuda a refactorizar y reestructurar el RTL en consecuencia, y realmente no desea hacer esto teniendo que cambiar todos sus módulos manualmente”.

Hacer un seguimiento de esto puede ser una pesadilla. "Piense en el control de revisión de un documento o archivo que forma parte de una jerarquía", dice Rance. “Es posible que tengas múltiples versiones o revisiones de esa jerarquía, dependiendo de lo que estés haciendo. Es posible que tenga un equipo de verificación que realice análisis de PPA y descubra que si lo modifican un poco y crean otra versión de esta jerarquía, funciona mejor. Tienes que hacer un seguimiento de eso”.

Por mucho que las jerarquías nos ayuden a dividir y conquistar, algunas cosas desafían cualquier intento de hacer estas simplificaciones. "Cosas como el análisis térmico deben realizarse en todo el chip", dice Schirrmeister de Arteris. “Pero es necesario poder correlacionar esto con lo que sucede funcionalmente en el chip, con los datos que lo atraviesan. Desea poder tomar una fotografía del chip, donde observaría los puntos de acceso y dónde se encuentra cada pieza de funcionalidad, potencialmente desde una perspectiva del ciclo de vida, y siendo el que más se verá afectado. Correlacionar esto con los datos está lejos de ser trivial”.

Otras jerarquías

Existen otras jerarquías, como una jerarquía funcional. Lo más cercano que tenemos a esto hoy es un sistema de seguimiento de requisitos que comienza con definiciones de alto nivel de lo que debería hacer un sistema. Éstas se dividen en tareas cada vez más simples, hasta que finalmente se identifica la lógica u otros circuitos que realmente las proporcionan, junto con los bancos de pruebas que verifican que se cumpla el requisito adecuado.

Algunas jerarquías van y vienen durante el proceso de diseño. "Es posible que tenga una jerarquía para el árbol del reloj", dice Schirrmeister. “Existe la jerarquía para el sistema de distribución de energía. Y luego hay una jerarquía vista por las herramientas de análisis de sistemas sobre cómo conectan todo para obtener una perspectiva completa del chip. Lo que pensamos con ESL (nivel de sistema electrónico) fue esta noción de una especificación funcional ejecutable que describe todo. Esto es algo que todavía no ha trascendido. De alguna manera, parece que nos salimos con la nuestra, lo cual es sorprendente”.

El diseño físico proporciona otra jerarquía. En el nivel más alto se encuentra la planificación del piso, que utiliza la jerarquía estructural como punto de partida. Estos bloques se colocan y la interconexión se encamina entre ellos. Cada bloque se presenta mediante síntesis física, que a su vez se ocupa de la interconexión local. 3D-IC agregará una nueva dimensión a esto, donde ahora puede existir enrutamiento en la dirección Z.

"A medida que empecemos a ver que los sistemas 2.5D y 3D basados en chiplets reemplazan los diseños de sistema en un chip (SoC), la jerarquía no será tanto una construcción estratégica como una representación de la realidad física", dice LaBorde de Cadence. “Las macros en un esquema podrían representar chips en un sistema, cada uno en su propio proceso único. Las conexiones entre ellos serán soldaduras en lugar de pines simbólicos en un diseño”.

Conclusión

Si bien no es perfecta, la descomposición estructural informal que se utiliza hoy en día ha demostrado ser una jerarquía hábil. Algunos aspectos de un flujo se ven afectados por ello, pero la mayoría son capaces de utilizarlo eficazmente y las herramientas pueden compensar sus deficiencias. Si bien existe una cierta cantidad de potencial de optimización que se pierde debido a esto, este es probablemente uno de los pequeños sacrificios realizados en nombre de la productividad.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiengineering.com/an-entangled-heterarchy/