Durante los GOMACTech conferencia celebrada en Carolina del Sur la semana pasada tuve una llamada de Zoom con Deepak Shankar, fundador y vicepresidente de tecnología de Mirabilis Design Inc. para hacer preguntas y ver una demostración en vivo de Simulación visual – una plataforma de modelado, simulación, exploración y colaboración para desarrollar electrónica y SoC. Lo que hace que VisualSim sea tan distintivo es que viene con alrededor de 500 bloques IP de alto nivel listos para usar, incluidos 35 procesadores ARM, unos 100 procesadores y más de 30 interconexiones diferentes. Los usuarios de VisualSim conectan rápidamente estos bloques de IP visualmente para crear sus sistemas, completos con redes. Un diseñador de automóviles puede modelar toda la red, incluidas las comunicaciones 5G, Ethernet, SDA y actualizaciones OTA con VisualSim.

Un modelo de alto nivel permite una exploración arquitectónica más rápida y hacer concesiones arquitectónicas, mucho antes de que la implementación comience con el código RTL. Puede modelar actividades complejas como un bus, memorias e incluso caché, midiendo aspectos como retrasos y latencia de un extremo a otro. Los ingenieros pueden medir cuál es su proporción de aciertos/errores de caché y qué sucede con las solicitudes a las cachés L2. Se modelan todos los protocolos de red populares: AXI, CHI, CMN600, Arteris NOC, UCIe, etc.

Con este enfoque de modelado, un arquitecto puede modelar un SoC, un avión completo o un sistema automotriz y luego comenzar a medir su rendimiento para ver si cumple con los requisitos. VisualSim es un simulador multidominio que puede integrar sistemas analógicos, de software, de energía, digitales y de redes en un solo modelo.

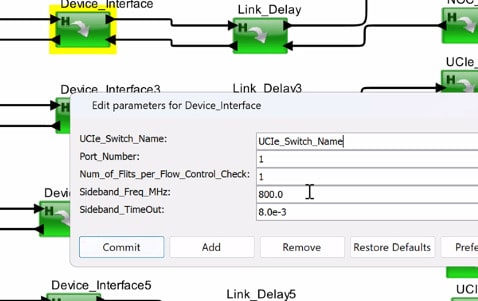

Para la demostración en vivo, Deepak me mostró un diseño basado en chiplets que tenía chips separados para el DSP, la GPU, el procesador de IA y la CPU, todos conectados entre sí mediante UCIe, y cada bloque de IP estaba parametrizado para permitir la personalización y la exploración.

Al presionar el bloque UCIe había una IP llamada conmutador UCIe, y un usuario puede personalizar este bloque con cinco parámetros, todos en un alto nivel.

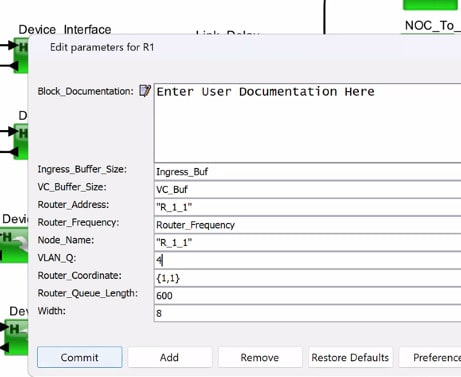

Un bloque de IP de enrutador tenía 10 parámetros para personalización.

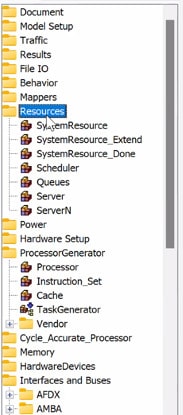

Para encontrar cada bloque de IP había una lista desplazable en el lado izquierdo de la GUI, con cada familia de IP en la biblioteca. En cuestión de segundos podrás navegar, seleccionar y comenzar a personalizar una IP.

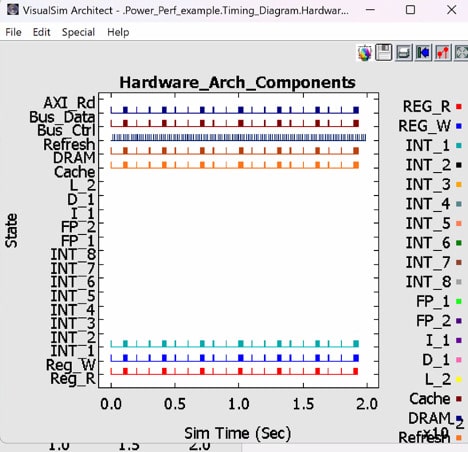

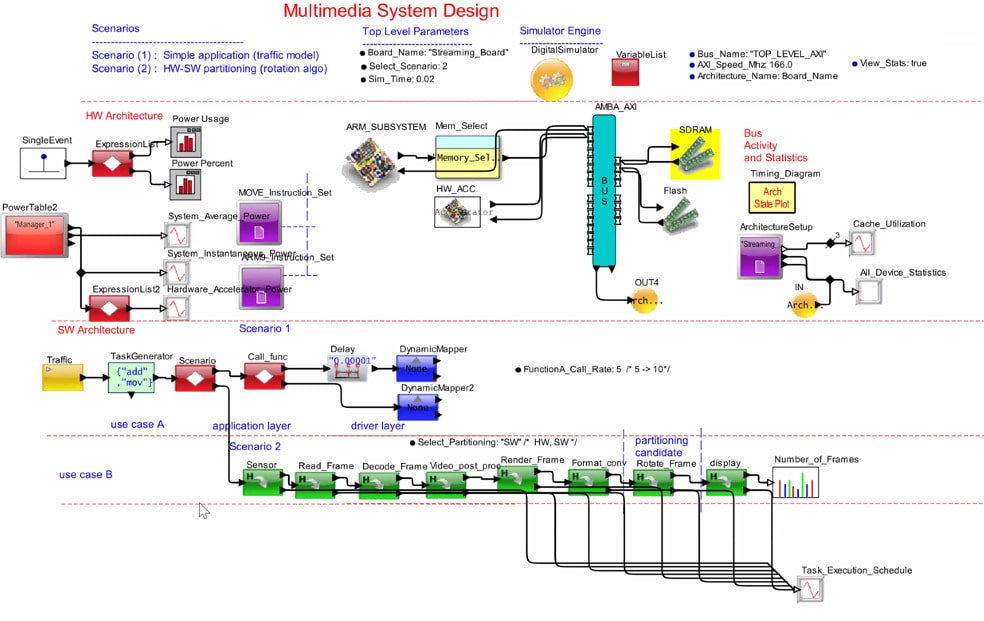

En VisualSim estás conectando cada IP en el flujo de datos, manteniéndote en un nivel alto. La siguiente demostración en vivo fue para el diseño de un sistema multimedia, y para simular 20 ms se necesitaron aproximadamente 15 segundos de tiempo en la pared, ejecutándolo en una computadora portátil. Mientras se ejecuta la simulación, puede ver el rendimiento del sistema como energía instantánea, medir la utilización de la canalización, la utilización de la memoria caché, el uso de la memoria e incluso ver un diagrama de tiempo. Esta simulación en tiempo real desencadenó 7.5 millones de eventos y el cliente construyó este modelo en menos de dos semanas, que incluía todo el SoC.

Otro ejemplo de cliente que mencionó Deepak incluye 45 masters y se completó en aproximadamente 4 semanas, completamente probado.

Puede mirar dentro de cualquiera de los bloques de IP y analizar métricas como pasa/falla y luego comprende por qué falló. Incluso hay un motor de inteligencia artificial para ayudar a analizar datos de manera más eficiente, como encontrar un desbordamiento del búfer que causó una falla. Mientras su modelo se ejecuta, se capturan análisis para ayudar a medir el rendimiento del sistema e identificar cuellos de botella arquitectónicos.

VisualSim se actualiza dos veces al año y luego hay actualizaciones de parches para cuando se agregan nuevos bloques de IP. Un arquitecto define los requisitos en un archivo de Excel, con métricas como límites de latencia y ocupación del búfer.

Los usuarios de VisualSim pueden definir el rango de tamaño de carga útil en términos de bytes, rangos de velocidad y valores preferidos. El modelo de su sistema se puede recorrer a través de las combinaciones para encontrar el mejor conjunto de parámetros. El simulador incluso sabe cómo explorar los valores mínimo, máximo y preferido. Puedes definir qué parámetros del sistema se explorarán. A continuación se mostró una demostración del sistema multimedia y luego se simuló en vivo.

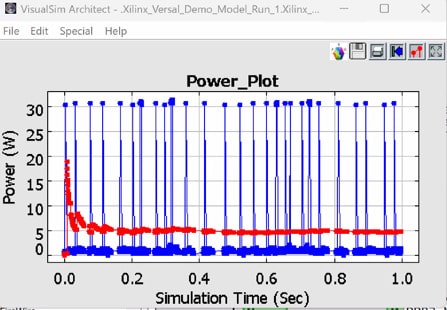

Para un bloque FPGA, usted elige el proveedor y el número de pieza, y luego puede ver la latencia de cada tarea y las estadísticas del canal del NOC después de ejecutar una simulación. Se mostró un gráfico de potencia durante 1 segundo de operación cuando se utilizan piezas Xilinx Versal.

Todas las demostraciones en vivo se realizaron en una computadora portátil con Windows. Otros sistemas operativos compatibles son: Unix, Mac. Ejecutar VisualSim requiere una infraestructura de HW mínima, porque los modelos son de alto nivel.

Los usuarios de VisualSim reciben más de 500 ejemplos prediseñados para ayudarle a comenzar rápidamente, como un sistema de comunicación completo con antena, transceptor, FPGA con banda base e interfaz Ethernet. Los arquitectos de sistemas que utilizan VisualSim pueden colaborar con todos los especialistas de bajo nivel, como los diseñadores de RTL.

Las compensaciones a nivel de sistema se pueden modelar y evaluar, como:

- Cambio de modulación 64-QAM a QPSK

- Procesador más rápido a más lento

- Cambiar las especificaciones de Ethernet

Si comienza con VisualSim para modelar, implementar y luego medir, espere ver un 95% de precisión en comparación con los resultados de la implementación RTL. La promesa de utilizar modelos de alto nivel es eliminar los problemas de rendimiento antes de la implementación o integración. Realmente no se requiere codificación para un modelo de sistema completo.

Mirabilis tiene hasta el momento 65 clientes en todo el mundo y unos 250 proyectos completados. Algunos de los clientes conocidos incluyen: NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

Resumen

En los viejos tiempos, un diseñador de sistemas podía haber dibujado sus ideas en una servilleta mientras comía en un restaurante y luego volver a trabajar y improvisar algunas hojas de cálculo de Excel con ecuaciones arcanas para crear un modelo. Hoy hay una nueva opción, y es dar Simulación visual de Mirabilis es un intento. Ahora puede modelar un sistema completo en tan solo unas pocas semanas, además de realizar compensaciones arquitectónicas mientras ejecuta simulaciones reales, todo antes de entrar en detalles detallados de implementación.

Blogs relacionados

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/