En el pasado, analistas, consultores y muchos otros expertos intentaron estimar el coste de un nuevo chip implementado con la última tecnología de proceso. Llegaron a la conclusión de que, con el nodo de 3 nm, sólo unas pocas empresas podrían permitírselo, y cuando llegaran al rango de angstrom, probablemente nadie lo haría.

Mucho ha cambiado en los últimos nodos de proceso. Un número cada vez mayor de empresas emergentes están construyendo con éxito chips de nodos avanzados por mucho menos dinero que las cifras tan cotizadas. Detrás de las cifras se esconden algunos cambios de amplia base en el diseño y la fabricación de chips. Entre ellos:

- Muchos chips de nodos avanzados son conjuntos altamente replicados de elementos de procesamiento de acumulación múltiple utilizados para IA/ML. Son relativamente simples en comparación con la integración de diferentes componentes en una sola matriz, donde es necesario caracterizarlos por problemas térmicos, ruido y diversos casos de uso y aplicaciones.

- El empaquetado avanzado, que se ha generalizado desde que se generaron esas primeras estimaciones, permite a los fabricantes de chips agrupar chips o chiplets desarrollado en diferentes nodos de proceso, en lugar de intentar llevar las funciones analógicas a 5 nm y más, lo cual es costoso y no beneficioso.

- En el pasado, pasar al nodo más reciente garantizaba el liderazgo del mercado en cuanto a rendimiento y potencia. Ese ya no es el caso. Las mejoras en los nodos maduros y los cambios arquitectónicos que involucran hardware y software permiten a muchos fabricantes de chips retrasar la migración a los nodos más nuevos al menos hasta que esos procesos estén lo suficientemente maduros como para ser rentables.

Uno de los grandes problemas de las primeras estimaciones es que eran extrapolaciones de los mejores datos disponibles en ese momento. La fuente predominante fue la Hoja de Ruta Tecnológica Internacional para Semiconductores, que se eliminó gradualmente en 2016. En los años siguientes, los fundamentos del diseño y la fabricación de chips cambiaron drásticamente.

Por ejemplo, muchos asumieron que todos los chips nuevos llenarían una retícula y que el tamaño y la complejidad de los diseños seguirían creciendo. En algunos casos, la complejidad aumentó, mucho más allá del punto en el que todas las funciones más recientes caben en una sola retícula, pero muchas de esas nuevas funciones se desarrollan utilizando una combinación de las últimas geometrías de proceso y nodos de proceso establecidos. En otros, el número de elementos de procesamiento en un paquete aumentó, pero la complejidad en realidad disminuyó.

El software es otro elemento definitorio. No todo el software necesita desarrollarse desde cero. Además, existe una gran cantidad de herramientas y ecosistemas preexistentes para diseños Arm, NVIDIA y, cada vez más, RISC-V. Y casi todas las grandes empresas de EDA están invirtiendo fuertemente en AI/ML para acortar y mejorar el proceso de diseño, particularmente cuando se trata de depuración de software y aprovechar de manera más efectiva la experiencia en una empresa a través del aprendizaje reforzado.

Los números

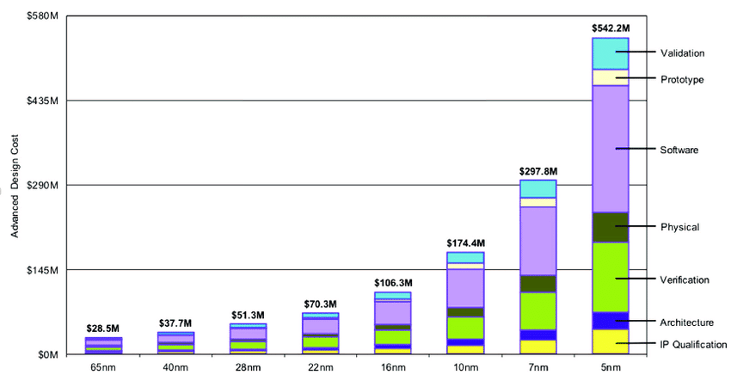

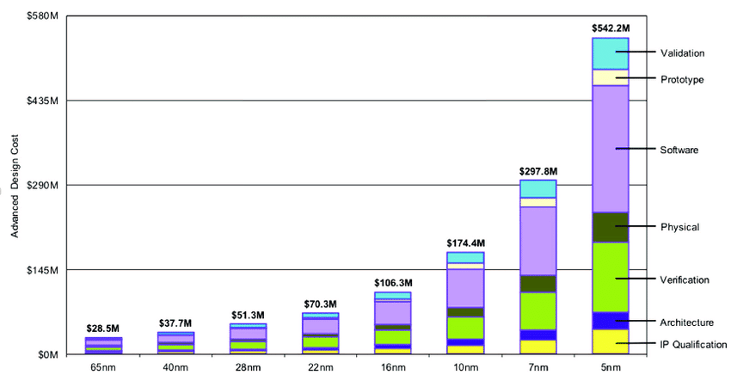

En 2018, la última vez que alguien hizo una estimación de este tipo, IBS publicó el gráfico que se muestra en la figura 1. Esto fijó el costo de un chip de 5 nm en 542.2 millones de dólares. Si eso fuera cierto, claramente solo se producirían dos o tres chips hoy en día, y probablemente nadie miraría más allá de los 3 nm.

Fig. 1: Costos de producir un nuevo chip. Fuente: SII 2018

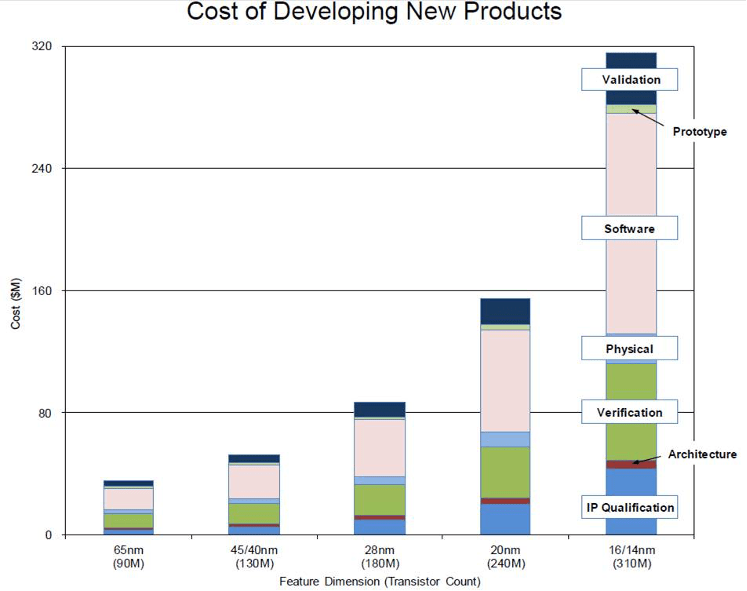

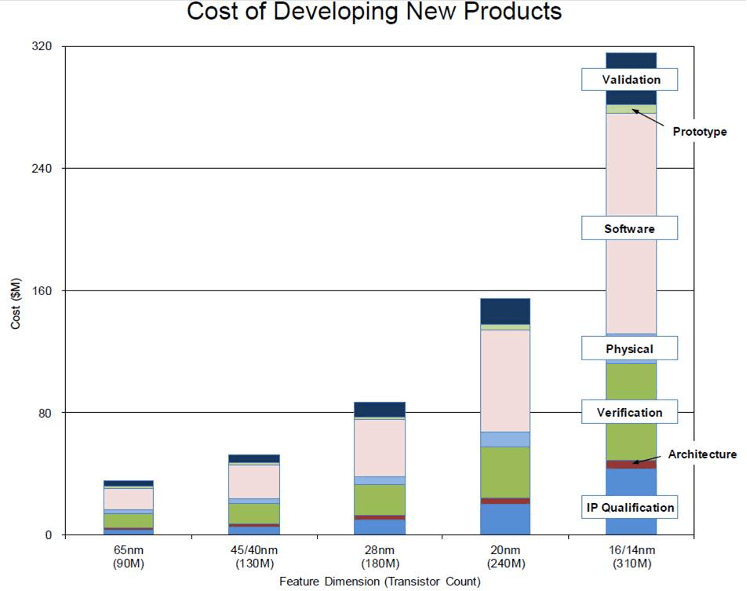

Si retrocedemos unos años y lo comparamos con el gráfico que el IBS produjo en 2014 (ver figura 2), podemos ver cómo esas estimaciones cambian con el tiempo.

Fig. 2: Costos de producir un nuevo chip. Fuente: SII 2014

Tenga en cuenta que el coste estimado de 16 nm/14 nm pasó de unos 310 millones de dólares a 106 millones de dólares. Y retrocediendo más en el tiempo, 28 nm pasó de unos 85 millones de dólares a 51 millones de dólares. Es un tema de debate si se trata de un exceso en los costos estimados o si refleja una disminución muy pronunciada de los costos una vez que un nuevo nodo ha madurado. Pero si las últimas cifras se descuentan en una cantidad similar, eso situaría el coste de un chip de 5 nm en el rango de 280 millones de dólares, y un chip de 7 nm en unos 160 millones de dólares.

"Considere Qualcomm o NVIDIA", dice Isadore Katz, director senior de marketing y desarrollo empresarial de Software de Siemens Digital Industries. “Si realmente costó 542 millones de dólares construir un nuevo chip, ellos y algunos otros podrían ser los únicos que realmente podrían permitirse el lujo de hacerlo. Pero no van a construir un chip de 5 nm. Tomarán una arquitectura, harán algunas innovaciones en esa arquitectura como parte de la transición al nuevo nodo de proceso y luego desarrollarán una familia de piezas que operan en ese nodo de proceso”.

Pocas empresas publican sus costos reales, pero se puede observar la financiación de riesgo recibida por las empresas y encontrar un costo bruto al observar cuánto dinero gastaron cuando se lanzó su primer chip. "Innovium se construyó con 150 millones de dólares para su chip inicial, y luego recibieron otra ronda de 100 millones de dólares, que financió varias generaciones", dice Nick Ilyadis, director senior de planificación de productos de Achronix. “Desde su fundación en 2014, Innovium recibió un total de 402 millones de dólares en financiación en 10 rondas, y todavía tenía 145 millones de dólares en efectivo disponibles cuando se vendió a Marvell en 2021 por 1 millones de dólares. Su tercera generación de chips se fabricó mediante un proceso de 7 nm”.

Una parte importante del costo es una penalización para el primero en actuar. "Los gastos asociados con los grandes chips digitales se han disparado", afirma Marc Swinnen, director de marketing de productos de Ansys. “De ahí provienen esas grandes cifras de los titulares. Si nos fijamos en lo que le toma a Apple crear un nuevo chip, son 18 meses, cientos de diseñadores, licencias, un conjunto de máscaras completamente nuevo y procesos avanzados. Ahí es cuando los costos aumentan. Pero si puedes usar un nodo más antiguo, esos costos son mucho menores ahora”.

También hay varios costos que podrían estar ocultos en esas cifras. "Se necesita una inversión masiva para volver a caracterizar la funcionalidad del nuevo transistor, implementar las capacidades de fabricación de máscaras, comprender los problemas de fabricación y crear los modelos de extracción", dice Katz de Siemens. “Pero estamos aprovechando las lecciones aprendidas en nodos anteriores y una vez que hayamos terminado con esos componentes básicos, el modelo BSIM-CMG, el modelo de extracción, las variaciones de chip y la metalización, podremos aprovechar los parámetros parametrizados. o procesar tecnología independiente que tenemos en las capas superiores”.

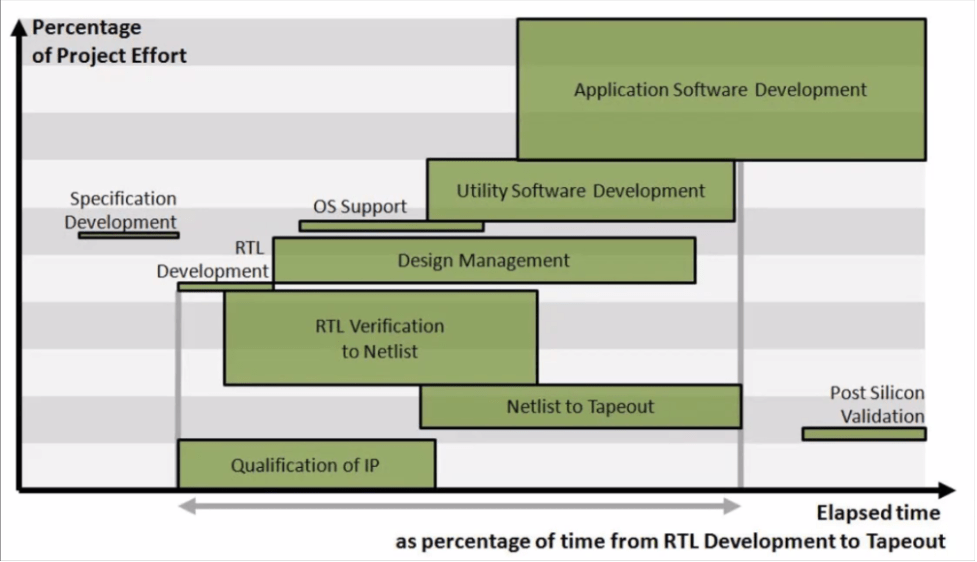

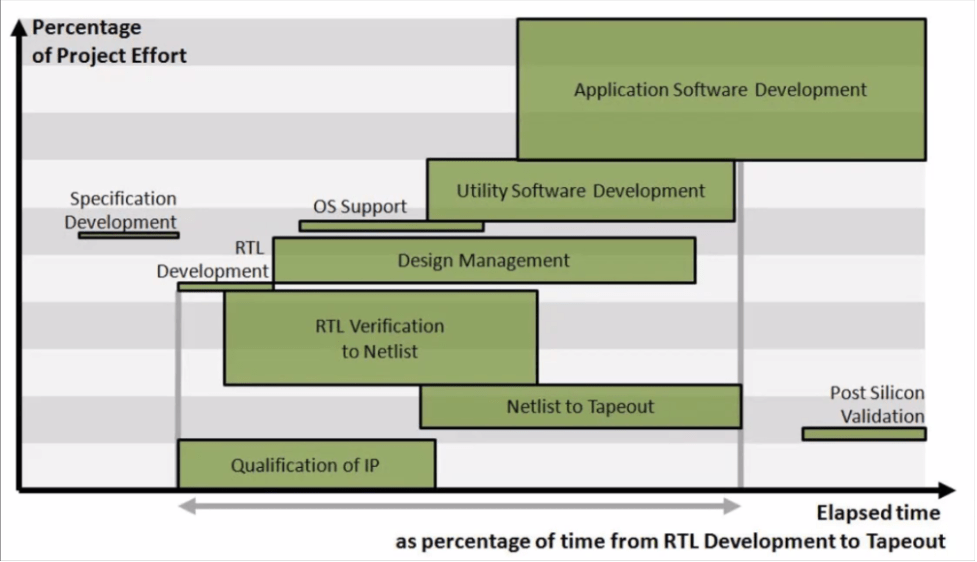

Los números han despertado la curiosidad de otros. "Este es un gráfico (ver figura 3) que creé hace 12 años", dice Frank Schirrmeister, vicepresidente de soluciones y desarrollo comercial de arterisa. “Había recibido cuatro o cinco conjuntos de datos de IBS, pero no podía publicar las cifras, por lo que el gráfico que creé promedió las categorías de gastos. Esto muestra los principales pasos en el desarrollo de chips. Muestra una línea de tiempo desde el desarrollo RTL hasta la salida en cinta a lo largo del eje x. Y luego el porcentaje del esfuerzo general del proyecto está en el eje y”.

Fig. 3: Tiempo y esfuerzo para crear un chip. Fuente: Frank Schirrmeister

Con base en la figura 3, puede considerar si alguno de estos cambia con el tiempo o escala con el tamaño o el nodo de producción. Por ejemplo, a menudo se afirma que el costo de la verificación aumenta cuadráticamente con el tamaño, aunque históricamente se ha demostrado que esto no es cierto. "Los costos de verificación aumentan porque cuanto más grande es el diseño, más tiempo lleva simularlo y más casos de prueba hay que generar", dice Ilyadis. “Hay pruebas de referencia que puedes usar de generaciones anteriores y continúas ejecutándolas. Luego están las nuevas pruebas asociadas con la funcionalidad adicional que se está agregando. Eso requiere más servidores, servidores más grandes, más discos. Se propaga a través de la infraestructura como costos adicionales”.

¿La infraestructura está incluida en los costos publicados? "El problema está en los detalles a la hora de entender qué hay en esos números", dice Schirrmeister de Arteris. “¿Está todo el software incluido en eso? ¿Cuánto nuevo desarrollo RTL hay ahí? ¿Cuánta verificación? ¿Necesitas comprar un emulador? Cuando se analiza el costo de las máscaras, eso al menos alcanza el orden de magnitud de estos chips”.

Algunos costos disminuyen con el tiempo. "Cuando se considera el costo de la propiedad intelectual, hay que desarrollarla, lo que utiliza recursos de ingeniería internos, o licenciar, lo que significa pagar al proveedor", dice Ilyadis. “Normalmente, las licencias vienen con soporte y mantenimiento, es decir, los desembolsos en efectivo. Luego están los costos de las herramientas. Cada generación requiere nuevos conjuntos de herramientas, porque el enrutamiento se vuelve más complejo o hay cosas adicionales a considerar. Está la plantilla del equipo que está desarrollando el chip. Además, debe construir dispositivos de prueba o incluso un producto que demuestre su chip. Ahora vamos más allá del chip en sí, pero son todas las cosas relacionadas con el desarrollo real del chip y lo que se necesita para llevarlo al mercado. Luego está ese regalo que sigue dando: el software. La mayoría de estos chips tienen algún tipo de programabilidad. Además de eso, está la fabricación, incluidos los probadores, los accesorios de prueba y los accesorios de precalentamiento para realizar pruebas de vida acelerada”.

Incluso los costos de propiedad intelectual pueden ser una variable significativa, especialmente si se considera el ahorro de tiempo que se obtiene al comprar propiedad intelectual o los costos indirectos asociados con el desarrollo de la propiedad intelectual. "El aumento del coste y la complejidad de los diseños de SoC está ejerciendo más presión sobre la infraestructura informática", afirma Brian Jeff, director senior de gestión de productos de BrazoLínea de Negocio de Infraestructura. “Esto está impulsando una tendencia hacia el silicio personalizado con el fin de proporcionar procesamiento especializado para cargas de trabajo específicas y obtener ahorros de eficiencia a escala. Al desarrollar IP con una base personalizable, permite al proveedor de IP asumir muchas de las tareas comunes de integración, verificación y validación que los socios han tenido que repetir diseño tras diseño. Esto libera a los socios para concentrar sus recursos en las características que los ayudarán a diferenciarse y dar forma a un diseño de chip completo para su carga de trabajo. En un ejemplo, un socio redujo el costo de su desarrollo de SoC de infraestructura de alta gama en 80 años de ingeniería”.

Muchos de los costos son incrementales. "No volvemos a aprender todo entre los nodos del proceso", dice Katz. “Recordamos las cosas que tenemos que hacer. Hemos invertido mucho en la parametrización o en la representación de los artefactos de diseño desde lo más alto, el banco de pruebas, la forma en que describimos la IP y la forma en que articulamos la lógica personalizada y los aceleradores hasta cómo diseñamos. las celdas. Entendemos dónde tenemos que hacer ajustes y tenemos diales y perillas donde podemos corregirlos. Nadie empieza desde cero entre nodos. Incluso si cambiamos la forma en que funcionan las superficies de los transistores, o reorganizamos la forma en que funcionará el metal de personalización de primer nivel, necesitamos dedicar más tiempo a caracterizarlo. Necesitamos dedicar más tiempo a comprender cómo extraerlo, y es posible que tengamos que hacer pequeños y modestos ajustes en los diseños de nuestras células para adaptarlo. Pero la topología básica está ahí”.

La propiedad intelectual bien desarrollada será reutilizable en múltiples generaciones de chips. Empresas como Intel, AMD, Marvell, Broadcom, NVIDIA y Qualcomm desarrollan gran parte de su propiedad intelectual internamente. Parte de esto se encuentra en forma de chiplets, que pueden caracterizarse completamente y reutilizarse en arquitecturas predeterminadas. La compensación es la experiencia interna, pero también hay menos sorpresas en el campo y no hay costos de licencia.

Costo de la EDA

Cada nodo crea algunos problemas y desafíos nuevos, y eso a menudo requiere una inversión significativa por parte de los proveedores de EDA en nuevas herramientas o la creación de flujos. Cuando el nodo es nuevo, muchas de esas herramientas son toscas y las soluciones se improvisan con cualquier tecnología que se pueda aplicar al problema.

Con el tiempo, la industria aprende qué funciona y qué no, y los flujos mejoran y eventualmente se automatizan. "Muchos desafíos se superan con fuerza bruta", dice Swinnen de Ansys. “Tomaron las herramientas disponibles y con una masa de gente suficiente y lo hicieron funcionar. Esto requería una estrecha colaboración con los proveedores. No es un flujo que se pueda dar a los diseñadores de chips habituales. Con el tiempo, aprendemos de ellos y ellos aprenden de nosotros. Las herramientas mejoran, se automatizan más, las asperezas se han solucionado y los pasos manuales intermedios se han reducido. Eso hace que la productividad sea mucho mayor”.

Sin embargo, lo que funciona hoy puede no funcionar en el futuro. "Hay una serie de cosas que hay que planificar", afirma Katz. “He estado involucrado en sincronización, variación de procesos y rebote del terreno. Cuando reduce sus umbrales de voltaje por debajo de 1 V, muchas de estas cosas se convierten en problemas. Eso era desconocido cuando estábamos entrando en los 14 nm. Hoy se entiende. La gente entiende lo que puede salir mal en el momento o en la disposición del diseño. Entienden los factores que hay que tener en cuenta con respecto a la contribución de los metales al retraso y la sincronización, y también se han vuelto cada vez más conscientes de algunos de los efectos secundarios físicos, la sensibilidad al ruido de falla, la sensibilidad a fuga. Todo esto se suma al libro de jugadas. Y el libro de jugadas lo guía a través de cada uno de los errores de los últimos 10 o 15 años. ¿Cómo los abordas? ¿Cómo se automatizan? ¿O cómo los diseñas?

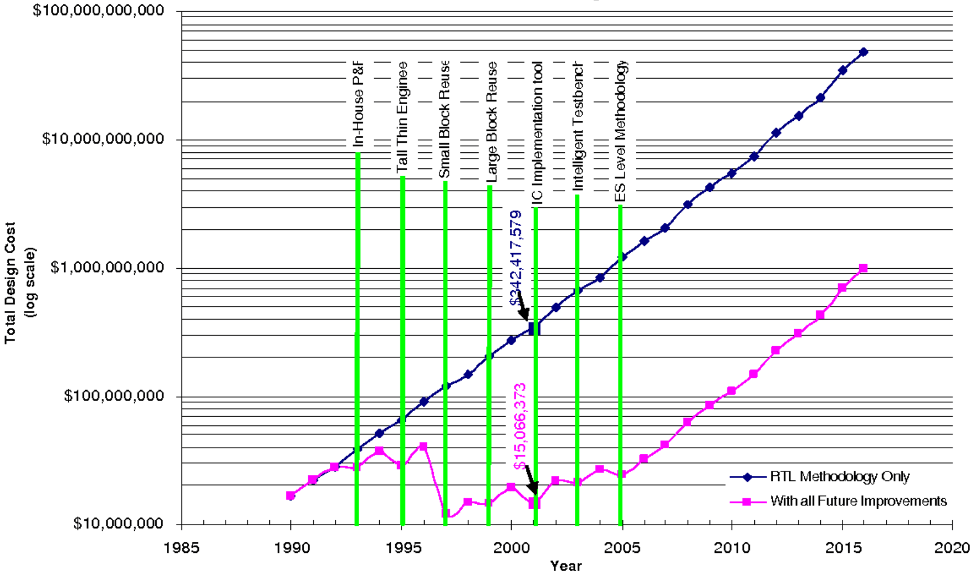

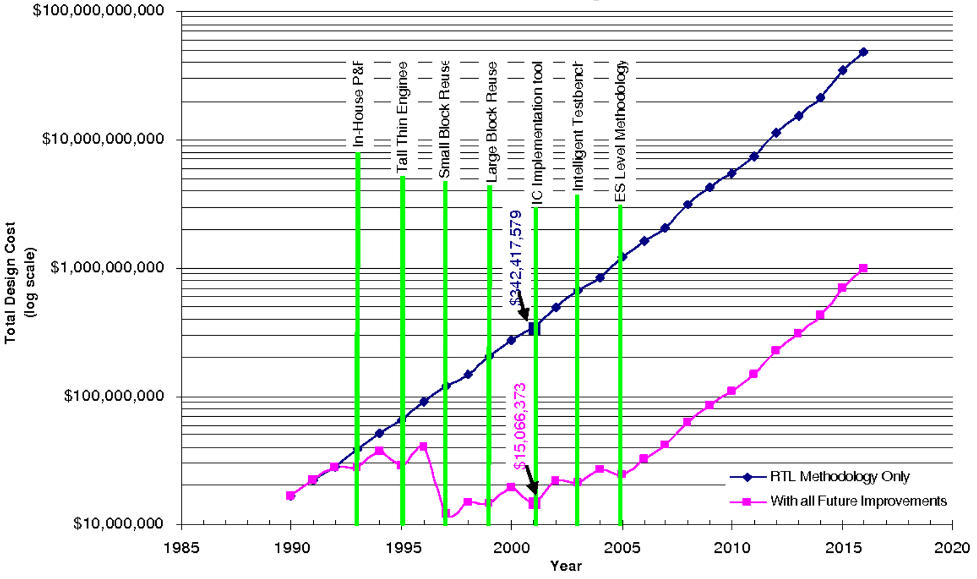

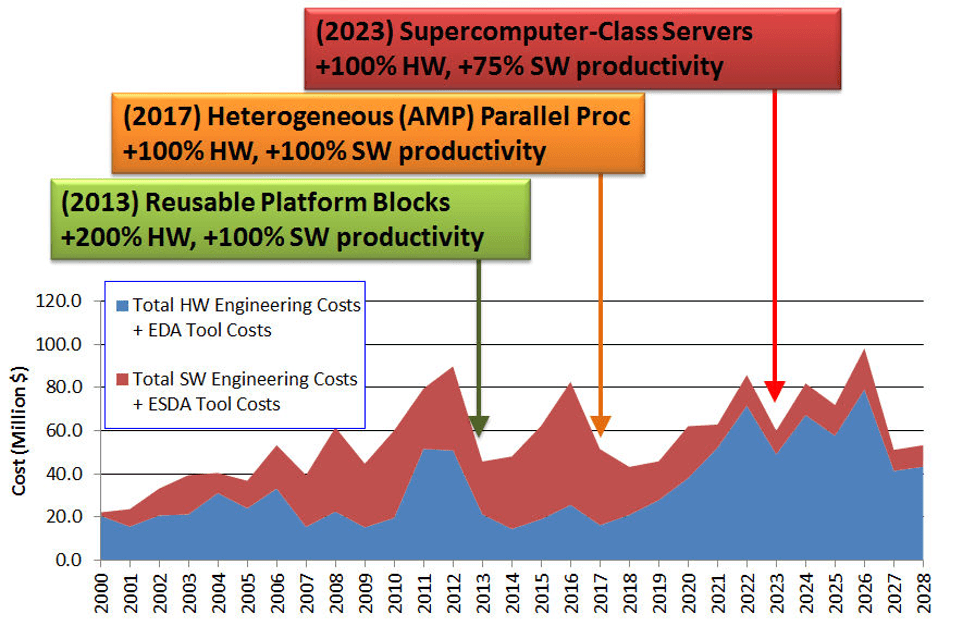

Otro gráfico antiguo que vale la pena revisar se muestra en la figura 4. Andrew Kahng y Gary Smith hicieron un análisis de los costos de diseño en 2001 para mostrar cómo los nuevos desarrollos de EDA estaban afectando la productividad. Esto fue publicado por el ITRS en 2002.

Fig. 4: Un nuevo modelo de costos de diseño para el SNTI 2001. Fuente: Actas del Simposio Internacional sobre Diseño Electrónico de Calidad 2002

Si bien esto muestra tecnologías del futuro que nunca surgieron, como ESL, otras tecnologías sí lo hicieron. Publicaciones posteriores del SNTI muestran que los costos de desarrollo permanecen algo estáticos, con sólo un ligero incremento con el tiempo. La Figura 5 (abajo) es su gráfico de 2013.

Fig. 5: Impacto de EDA en el costo de diseño de circuitos integrados. Fuente: Andrew Kahng, 2013

Los costos de desarrollo aumentan, especialmente para los nuevos nodos. "Las herramientas son cada vez más sofisticadas y tienen que adaptarse al tamaño del diseño", afirma Ilyadis. “Por lo general, esas herramientas actualizadas pueden agregar un 25% de costo de generación en generación, y ahí es donde las empresas de herramientas ganan dinero. Tienen que desarrollarse, tienen que trabajar en sus herramientas para hacerlas compatibles con la propiedad intelectual de próxima generación y con cualquier nuevo desafío que surja, por lo que le trasladarán ese costo de desarrollo a usted como una tarifa de licencia más alta”.

Pero ese no es el caso de los desarrolladores convencionales. "En la economía del diseño de semiconductores, el coste de las herramientas EDA nunca es una consideración clave", afirma Swinnen. “Es un elemento de costo del que alguien debe preocuparse, pero en la economía general del diseño de chips, EDA nunca es el factor decisivo. Es manufactura. Donde EDA impacta el costo del diseño es más en la productividad”.

Lo que estamos viendo es un rápido aumento de los costos de infraestructura asociados con las herramientas EDA. "Con la introducción de la IA en los conjuntos de herramientas, es fácil empezar a explorar más el espacio del diseño", afirma Schirrmeister. “Cada punto de datos en sus gráficos significa capacidad adicional y ciclos ejecutados en la nube. Para obtener la mejor implementación, ahora debe dedicar más esfuerzo informático. Lo que solía ser gente multiplicada por el tiempo y algunos costos de infraestructura, ahora se está convirtiendo en una redistribución de costos, donde el costo de computación en sí asume un papel mucho más importante en la ecuación de costos general”.

Conclusión

Ningún chip jamás desarrollado ha costado lo que se muestra en las cifras publicadas simplemente porque no existe ningún chip que realmente comience con una hoja de papel en blanco. Todo en esta industria se basa en la reutilización de la propiedad intelectual, parte de ella atada en bloques de IP, parte en modelos BSIM, parte en las cabezas de los ingenieros que inician una nueva empresa. Lo mismo, si no más, puede decirse de la industria del software, que siempre se basa en bibliotecas masivas de código.

Pero esas cifras están en el orden de magnitud correcto para diseños de vanguardia. Es importante comprender los costos totales asociados con el desarrollo y no centrarse solo en llegar a la finalización del silicio.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiengineering.com/what-will-that-chip-cost/