Los diseños de circuitos integrados tienen aplicaciones de verificación física como Layout Versus Schematic (LVS) a nivel de transistor para garantizar que el diseño y los esquemas sean equivalentes; además, existe una verificación de reglas eléctricas (ERC) para las conexiones a regiones de pozos denominada verificación suave. Las conexiones a todos los dispositivos deben tener las señales de voltaje más consistentes. Por lo tanto, el camino debe ser a través de las capas de metal para reducir la resistencia y factores como la caída de infrarrojos. La detección de conexiones pensó que otros materiales, como Wells, eran obligatorios. Los Soft-Checks son el método más comúnmente empleado para detectar esta situación. El calibre La línea de productos de Siemens es la herramienta más popular para las comprobaciones DRC y LVS, por lo que leí un artículo técnico de Terry Meeks para obtener más información sobre las comprobaciones suaves.

La conexión de dos capas metálicas en un diseño de circuito integrado requiere una alineación precisa de ambas capas metálicas y de la capa vía. Aquí hay una comparación usando una vista lateral y una vista de arriba hacia abajo donde el primer ejemplo no está conectado, porque Metal1 y Metal 2 no se superponen, mientras que el segundo ejemplo está conectado correctamente.

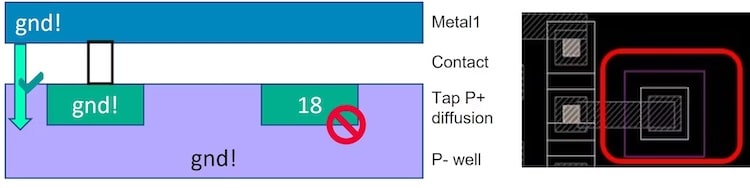

Queremos que nuestra herramienta ERC identifique errores de conectividad del pozo durante las comprobaciones suaves, para que puedan solucionarse. El siguiente diseño de IC tiene un error de conectividad y se muestra desde la vista lateral, donde la señal Metal1 enviada como Gnd está conectada a una región de difusión llamada difusión de derivación. En el lado derecho hay otra capa Metal1 con una difusión de grifo, pero esta conectividad crea una ruta de alta resistencia en Rwell a Gnd, y la verificación suave la marca como un error.

Otro ejemplo de error de conectividad leve ocurre en el diseño de IC a continuación, donde solo podemos aplicar un nombre por polígono. La red de alimentación digital VDD no puede coexistir con la red de alimentación analógica AVDD, y debemos separarlas en dos formas. Las comprobaciones suaves ayudan a detectar estos problemas.

Un diseño de circuito integrado con fuentes de alimentación tanto digitales como analógicas puede resultar bastante complejo de diseñar correctamente, por lo que es aún más importante realizar comprobaciones suaves.

Se incluyen comprobaciones suaves durante las ejecuciones de LVS y con Calibre nmLVS hay un informe de los resultados de la verificación suave, que luego se puede ver usando el Calibre RVE espectador.

Al hacer clic en los resultados de RVE, se le indica qué celda tiene el error de verificación suave, los nombres de red, los nombres superior e inferior y otras propiedades. Esta información ayuda a determinar qué corregir en el diseño del IC. Al hacer clic en una capa inferior como un PWell para obtener un error de verificación suave, se muestra la geometría en amarillo.

Para el mismo error de verificación suave, al hacer clic en la capa superior se muestra:

Durante la depuración, también puede mostrar todas las formas de la capa superior; las formas verdes son las formas de la capa superior neta seleccionadas, mientras que las amarillas son las formas de la capa superior neta rechazadas.

La depuración de errores de verificación suave con RVE implica hacer clic en la conectividad de las redes seleccionadas y rechazadas. Una ventana de información de red revela detalles como qué capas están involucradas y si a las formas les falta conectividad. Observar qué puertos están conectados a una red revela si faltan errores de VDD o GND. Este ejemplo muestra que la red 18 se rechaza porque le falta conectividad con Metal1.

Resumen

Las comprobaciones LVS son obligatorias para garantizar que un IC tenga un diseño libre de errores, y las comprobaciones suaves son parte de sus comprobaciones LVS. Existe un flujo de depuración comprobado de Siemens en su herramienta Calibre nmLVS que utiliza RVE para ayudar a los diseñadores de diseño a identificar rápidamente fallas en las comprobaciones suaves, de modo que los diseñadores puedan realizar correcciones y volver a verificar hasta que se pasen todas las comprobaciones. Siemens ha escrito un documento técnico para leer en línea, Detección y depuración de errores de conectividad de verificación suave.

Blogs relacionados

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/eda/342526-soft-checks-are-needed-during-electrical-rule-checking-of-ic-layouts/