Hoy en día se debate mucho sobre la eliminación de las barreras a la innovación. Los sistemas semiconductores son fundamentales para desbloquear muchas formas de innovación técnica, si tan solo pudiéramos abordar cuestiones como la desaceleración de la Ley de Moore, la reducción del consumo de energía, la mejora de la seguridad y la confiabilidad, etc. Pero hay otra barrera bastante sustancial que es el tema de este post. Es la dramática diferencia entre el rendimiento del procesador y de la memoria. Si bien los sistemas de CPU y GPU ofrecen niveles increíbles de rendimiento, las memorias que administran datos críticos para estos sistemas están rezagadas sustancialmente. Este es el problema del muro de la memoria, y me gustaría examinar cómo Arteris está desatando la innovación al romper el muro de la memoria. pared de memoria.

¿Qué es el Muro de la Memoria?

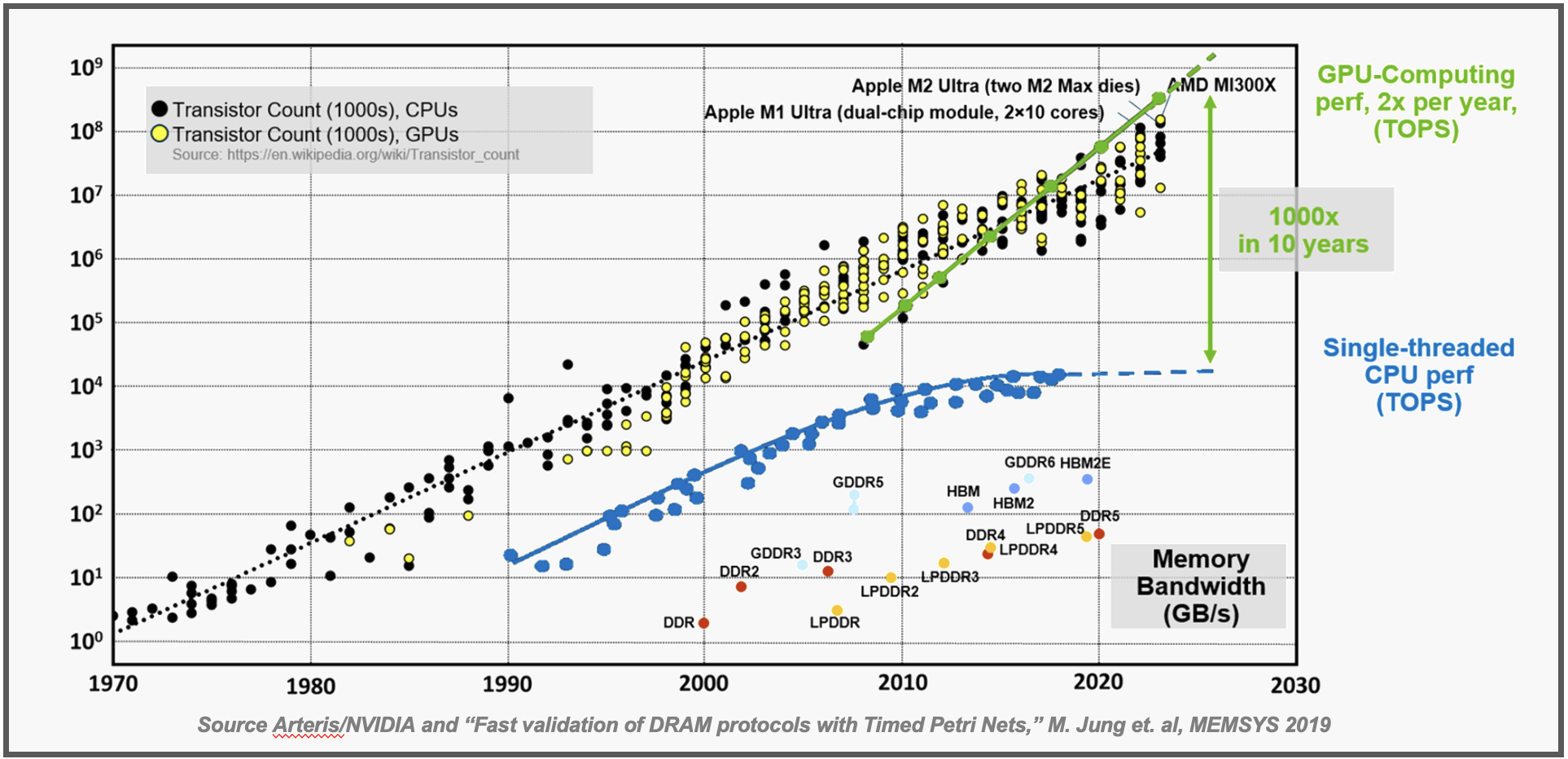

El gráfico en la parte superior de esta publicación ilustra el problema del muro de memoria. Puede ver el aumento constante en el rendimiento de las CPU de un solo subproceso representadas por la línea azul. La línea verde muestra el aumento exponencial en el rendimiento que agregan los grupos de GPU. Se estima que el aumento del rendimiento de las GPU frente a las CPU será 100 veces mayor en 10 años, una estadística alucinante. Como nota al margen, puede ver que el transistor cuenta tanto para las CPU como para las GPU agrupadas alrededor de una línea recta similar. El rendimiento de la GPU se consigue realizando menos tareas mucho más rápido en lugar de utilizar más transistores para solucionar el problema.

Muchos sistemas actuales son una combinación de varias CPU que realizan amplias tareas de administración con una gran cantidad de GPU que realizan tareas específicas, a menudo relacionadas con la IA. La combinación ofrece el sorprendente rendimiento que vemos en muchos productos. Hay un lado oscuro de esta arquitectura armoniosa que se muestra en la parte inferior del gráfico. Aquí, vemos los datos de rendimiento de las diversas tecnologías de memoria que brindan toda la información para que la procesen estos sistemas. Como puede ver, el rendimiento entregado es sustancialmente menor que el de las CPU y GPU que dependen de estos sistemas de memoria.

Este es el problema del muro de la memoria. Exploremos la forma única en que Arteris está resolviendo este problema.

El enfoque Arteris: un NoC coherente y de caché altamente configurable

Un enfoque bien aceptado para lidiar con una velocidad de acceso a la memoria más lenta es buscar previamente los datos requeridos y almacenarlos en un caché local. Acceder a los datos de esta manera es mucho más rápido: unos pocos ciclos de CPU frente a más de 100 ciclos de CPU. Es un excelente enfoque, pero puede resultar desalentador implementar todo el software y hardware necesarios para acceder a la memoria desde el caché y garantizar que los datos correctos estén en el lugar correcto en el momento correcto y sean consistentes en todos los cachés. Los sistemas que ofrecen eficazmente esta solución se denominan caché coherente, y lograr este objetivo no es fácil. Una implementación de coherencia únicamente de software, por ejemplo, puede consumir hasta ~25% de todos los ciclos de CPU en el sistema y es muy difícil de depurar. Los diseñadores de SoC a menudo eligen soluciones de hardware NoC coherentes con caché, que son transparentes para el software que se ejecuta en el sistema.

Recientemente, tuve la oportunidad de hablar con Andy Nightingale, vicepresidente de gestión de productos y marketing de arterisa. Andy hizo un gran trabajo explicando los desafíos de implementar sistemas coherentes de caché y la solución única que Arteris ha desarrollado para hacer frente a estos desafíos.

Resulta que el desarrollo de una arquitectura coherente de caché confiable y energéticamente eficiente afecta muchos aspectos de hardware y software del diseño del sistema. Hacer que todo funcione de manera confiable, eficiente y alcanzar los objetivos requeridos por el PPA puede ser bastante difícil. Andy estimó que todo este trabajo podría requerir 50 años de ingeniería por proyecto. Eso es mucho tiempo y costo.

La buena noticia es que Arteris tiene habilidades sustanciales en esta área y la compañía ha creado una arquitectura coherente de caché completa en uno de sus productos de red en chip (NoC). Andy describió Ncore, un NoC completo con coherencia de caché ofrecido por Arteris. La gestión del acceso a la memoria encaja bien en la arquitectura general de red en chip por la que Arteris es conocido. Ncore gestiona la parte coherente de caché del SoC de forma transparente para el software, lo que libera al diseñador del sistema para centrarse en los desafíos de nivel superior asociados con conseguir que la CPU y todas esas GPU realicen la tarea en cuestión.

Andy analizó una lista sustancial de capacidades de Ncore:

- Productivo: Conecte múltiples elementos de procesamiento, incluidos Arm y RISC-V, para obtener la máxima productividad de ingeniería y acelerar el tiempo de comercialización, ahorrando más de 50 años-persona por proyecto.

- Configurable: Escalable desde topologías heterogéneas a topologías de malla, compatible con interfaces coherentes CHI-E, CHI-B y ACE, así como ACE-Lite IO coherente. Ncore también permite que los agentes no coherentes de AXI actúen como agentes coherentes de IO.

- Integración de ecosistemas: Prevalidado con los últimos núcleos automotrices Arm v9, cumpliendo con una asociación previamente anunciada con Arm.

- Seguro: Cumple con los requisitos de ASIL B a ASIL D para aplicaciones de seguridad automotriz y cuenta con la certificación ISO26262.

- Eficiente: Área de matriz más pequeña, menor potencia y mayor rendimiento por diseño, en comparación con otras alternativas comerciales.

- Mercados: Adecuado para soluciones SoC de automoción, industriales, informática empresarial, de consumo y de IoT.

Andy detalló algunos de los beneficios que se logran con un diseño de SoC para el consumidor. Estos incluyeron una planificación simplificada de los chips gracias a la arquitectura altamente distribuida, lo que promueve la utilización eficiente de los recursos. La interconexión de alto rendimiento de Arteris con un tejido de baja latencia y alto ancho de banda garantizó una transferencia de datos perfecta y mejoró el rendimiento general del sistema.

Profundizando un poco más, Ncore también proporciona visibilidad en tiempo real del tejido de interconexión con seguimiento a nivel de transacciones, monitoreo del rendimiento y detección y corrección de errores. Todas estas características facilitan una fácil depuración y una calidad superior del producto. El soporte integral del ecosistema y la compatibilidad con interfaces estándar de la industria como AMBA también facilitan una integración más sencilla con componentes de terceros y herramientas EDA.

Esta fue una discusión muy útil. Parece que Arteris ha reducido drásticamente los gastos generales para la implementación de arquitecturas coherentes con caché.

Aprender Más

Mencioné algunos detalles sobre el trabajo que Arteris está haciendo con Arm. No crea que ese es el único socio con el que trabaja la empresa. Arteris ha sido llamada la Suiza del sistema IP. La compañía también tiene un trabajo importante con la comunidad RISC-V como detallado en la publicación de SemiWiki aquí.

Arteris anunció recientemente la expansión de su producto Ncore. Puedes leer como Arteris amplía la IP de interconexión coherente de caché Ncore para acelerar los diseños electrónicos de vanguardia aquí. En el comunicado, Leonid Smolyansky, Ph.D. El vicepresidente sénior de arquitectura, seguridad y protección de SoC de Mobileye ofreció estos comentarios:

“Hemos trabajado con la tecnología de red en chip de Arteris desde 2010, usándola en nuestras tecnologías avanzadas de conducción autónoma y asistencia al conductor. Estamos entusiasmados de que Arteris haya aportado su importante destreza de ingeniería para ayudar a resolver los problemas de tolerancia a fallas y diseño confiable de SoC”.

También hay un breve (un poco más de un minuto) vídeo que explica los retos que aborda Ncore. El vídeo me pareció bastante informativo.

Si necesita un rendimiento mejorado para su próximo diseño, definitivamente debería observar de cerca las soluciones coherentes de caché que ofrece Arteris. Puede Obtenga más información sobre Ncore aquí. Y así es como arterisa está desatando la innovación derribando el muro de la memoria.

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/ip/arteris/342991-arteris-is-unleashing-innovation-by-breaking-down-the-memory-wall/