La incesante demanda de SoC de menor potencia es evidente en muchos mercados. Los ejemplos incluyen dispositivos móviles, IoT y portátiles de última generación junto con las altas demandas informáticas para la IA y las comunicaciones 5G/6G. Los factores que influyen en el bajo consumo de energía incluyen la duración de la batería, la gestión térmica y, para aplicaciones de alta computación, el costo total de operación. Hay varios enfoques disponibles para lograr baja potencia. Un hilo común para muchos es la necesidad de una Foundation IP óptima, es decir, memorias integradas y bibliotecas lógicas. Esta es un área de importante inversión y liderazgo de mercado para Synopsys. Ahora hay dos publicaciones informativas disponibles para ayudarle a comprender las opciones y beneficios disponibles. Resulta que lograr un consumo de energía extremadamente bajo con los compiladores de memoria IP y las bibliotecas lógicas de Synopsys Foundation está al alcance de la mano.

Veamos la información que está disponible.

Boletín Técnico

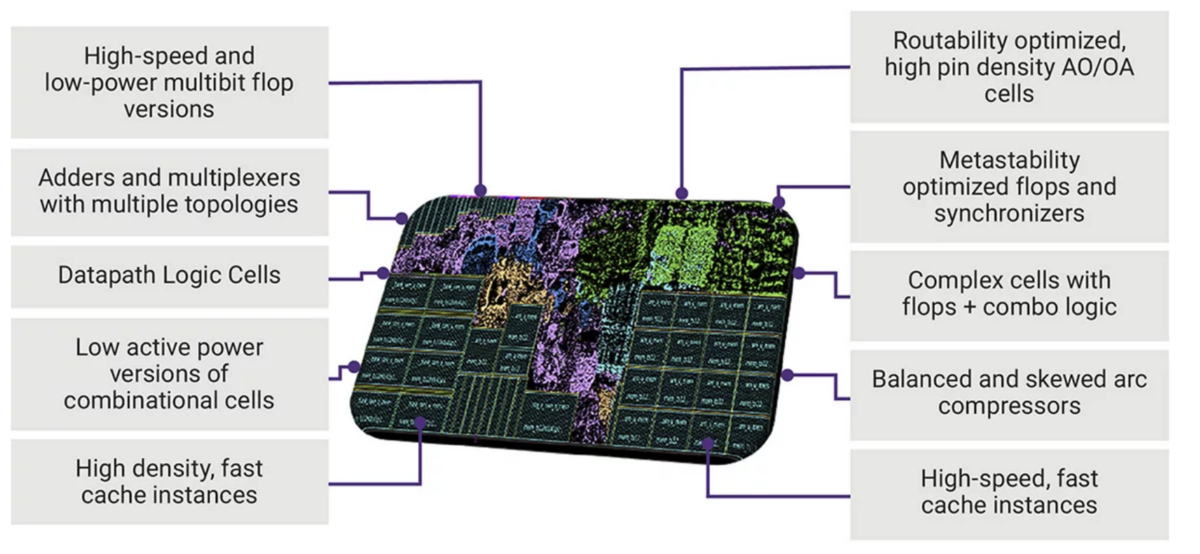

Voy a empezar con Optimización de PPA para aplicaciones HPC e IA con Synopsys Foundation IP, un boletín técnico que se centra en bibliotecas lógicas. El artículo proporciona detalles sobre la solución Foundation IP con reconocimiento de herramientas de Synopsys. Se analizan temas como circuitos optimizados, compatibilidad con un amplio rango de voltaje operativo y la flexibilidad para agregar optimizaciones específicas del cliente. El artículo también ofrece una perspectiva sobre cómo lograr el máximo rendimiento posible o la mejor relación potencia-rendimiento. La siguiente figura resume los circuitos de la biblioteca lógica disponibles en el kit de diseño HPC.

Se proporcionan detalles sobre cómo se logran las mejoras de energía en muchas aplicaciones y estrategias de diseño. Los temas que se tratan incluyen el escalado dinámico de voltaje en un amplio rango de voltaje operativo, la optimización de la IA y el PPA del bloque acelerador específico de la aplicación, soluciones para red en chip y cómo el kit de diseño Synopsys HPC se optimiza conjuntamente con Synopsys EDA para una implementación eficiente de SoC.

Este boletín técnico proporciona un rico conjunto de información y ejemplos. Puede accede a esta información aquí.

White Paper

También está disponible un documento técnico completo titulado, ¿Cuan bajo Puedes ir? Superando los límites de los transistores. Esta pieza profundiza tanto en los recuerdos integrados como en las bibliotecas lógicas. Examina los detalles detrás de lograr una potencia extremadamente baja. Se analizan varias áreas de aplicaciones, incluidas las móviles, Bluetooth e IoT, informática de alto rendimiento, automoción y criptografía.

Para las memorias integradas, se analizan varios enfoques, incluidas técnicas de asistencia y división de voltajes de suministro. Se señala que se requiere una cuidadosa cooptimización entre la tecnología y el diseño de circuitos de asistencia de memoria para ofrecer un funcionamiento de memoria denso y de bajo consumo a bajos voltajes. Se revisan varias técnicas de asistencia mejorada. Las mejoras en la potencia oscilan entre el 10% y el 37%.

También se analiza la confiabilidad de los recuerdos. El artículo explica que a medida que se reduce el voltaje, la celda SRAM comienza a mostrar degradación. Esta degradación puede causar múltiples problemas: las lecturas se alteran, el bitcell no se invierte, el SER es pronunciado, la detección falla, las señales de control se desvían y la señal BL se debilita. Por lo tanto, se necesitan técnicas de asistencia para soportar los voltajes extremadamente bajos requeridos por las aplicaciones de vanguardia de baja potencia.

Los enfoques que Synopsys adopta aquí marcan una diferencia significativa. Se discuten estrategias para mejorar la confiabilidad y métodos para simular el envejecimiento. Deberías leer los detalles por ti mismo: viene un enlace. Los datos muestran resultados convincentes, con cinco a diez años de vida añadidos.

También se analizan las bibliotecas lógicas, con estrategias para permitir el funcionamiento de voltaje muy bajo a 0.4 V o menos. También se revisa la optimización arquitectónica. Se pueden emplear técnicas de arquitectura de celda estándar para reducir la potencia tanto dinámica como de fuga. Por ejemplo, Synopsys utiliza técnicas arquitectónicas basadas en pila versus técnicas basadas en etapas para lograr la topología óptima para operaciones de bajo voltaje. Se presenta la estrategia detrás de este enfoque.

También se cubre la optimización de la caracterización. Una parte importante de la caracterización es la variación del proceso de modelado en un SoC, denominada variación en el chip (OCV). Aquí se emplean varias técnicas avanzadas, incluido el aprendizaje automático para aumentar la precisión y optimizar el rendimiento y la potencia.

El documento técnico concluye con una descripción general de cómo combinar todo a nivel de SoC para lograr un funcionamiento de bajo voltaje. Se analiza la reducción de voltaje, junto con técnicas de escalado dinámico de voltaje y frecuencia (DVFS) y varias estrategias de apagado, como el sueño ligero, el sueño profundo, el apagado completo y los modos POFF (periferia apagada).

Este documento técnico cubre una serie de temas de optimización de energía con excelente detalle. Lo recomiendo altamente. Puede consigue tu copia aquí. Y así es como lograr un consumo de energía extremadamente bajo con los compiladores de memoria IP y las bibliotecas lógicas de Synopsys Foundation está a nuestro alcance.

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/ip/341966-achieving-extreme-low-power-with-synopsys-foundation-ip-memory-compilers-and-logic-libraries/