La reutilización del diseño de IP de semiconductores ha permitido el crecimiento incesante de la complejidad de los sistemas basados en SoC y chiplets a lo largo de los años, y la reutilización de IP conlleva muchos desafíos únicos. Las empresas de diseño sin fábrica utilizan la propiedad intelectual proporcionada por un vibrante ecosistema de proveedores y fundiciones de propiedad intelectual, además de la reutilización interna en la búsqueda de llegar al mercado más rápidamente que comenzar desde cero. Las organizaciones de estándares Accellera y IEEE han abordado los desafíos de la reutilización del diseño IP a través del estándar IP-XACT, que se remonta a 2004, cuando se lanzó IP-XACT 1.0. El último estándar es IEEE 1685-2022, por lo que son 18 años de progreso e historia para la reutilización de IP.

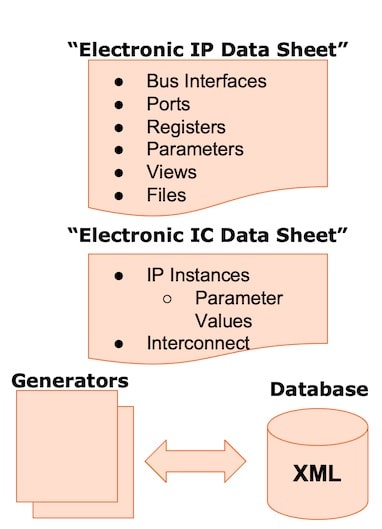

Hay un Webinar alojado por agnisys el 25 de octubre eso nos pone al día sobre IP-XACT 2022, y el presentador es Devender Pal Khari, miembro de Accellera Grupo de trabajo IP-XACT. El estándar IP-XACT define cómo los archivos en formato XML describen un bloque de IP para que las herramientas EDA y los flujos automatizados puedan comprender rápidamente elementos esenciales, como:

- Puertos

- Interfaces de bus

- Registros

- Elementos de la memoria

- Conexiones

- parámetros

- Jerarquía

Fuente: Tutorial IP-XACT de Accellera en DV Con US 2023 Los beneficios de utilizar un estándar como IP-XACT son que representa una única especificación para toda la información de IP, una única forma de definir los registros y todas las representaciones necesarias se pueden generar desde una única fuente mediante un flujo de trabajo automatizado.

Nuevo para IP-XACT 2022

El seminario web detalla los detalles técnicos de las últimas actualizaciones de la especificación, junto con los motivos de los cambios. El elemento condicional está presente se ha eliminado, pero por compatibilidad con versiones anteriores se admite a través de Accellera Vendor Extensions.

Se presentan ejemplos en tipoDefiniciones para mapas de memoria: memoriaMapDefinition y memoria MapDefinitionRef. También muestran cómo se utiliza la Tight Generator Interface (TGI) para comunicarse entre el entorno de diseño y los generadores.

Los dominios de energía utilizados en el Formato de energía unificado (UPF) se muestran con el elemento instancias de componente. Las restricciones de energía se admiten con elementos denominados powerConstraint y powerDomainRef.

Ahora se admiten modos definidos por el usuario para permitir condiciones en configuraciones dinámicas. Luego se hace referencia a estos modos en elementos de memoria, puertos, dominios de energía e interfaces. Se muestran ejemplos de modos definidos en un puerto y dominios de energía vinculados según los modos.

Resumen

Agnisys se ha centrado en la automatización EDA para interfaces HW/SW desde 2007 y es miembro activo del grupo de trabajo IP-XACT, por lo que tiene la experiencia para ayudar a los diseñadores de SoC a utilizar metodologías que admitan la reutilización de IP.

La seminario web de Agnisys en IP-XACT 2022 es el 25 de octubre, de 9 a. m. a 9:45 a. m. PDT, y el registro está en línea. Los ingenieros que utilicen IP-XACT se beneficiarán de los ejemplos que muestran lo que ha cambiado en la última versión y luego comenzarán a actualizar su metodología. Este es un seminario web técnico para que los ingenieros mejoren sus habilidades y comprensión.

Blogs relacionados

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/eda/336885-an-update-on-ip-xact-standard-2022/