Los chiplets están atrayendo una atención renovada en el mercado automotriz, donde la creciente electrificación y la intensa competencia están obligando a las empresas a acelerar sus cronogramas de diseño y producción.

La electrificación ha encendido el fuego en algunos de los fabricantes de automóviles más grandes y conocidos, que luchan por seguir siendo competitivos frente a ventanas de mercado muy cortas y requisitos en constante cambio. A diferencia del pasado, cuando los fabricantes de automóviles solían ejecutar ciclos de diseño de cinco a siete años, la última tecnología en los vehículos de hoy bien puede considerarse obsoleta en varios años. Y si no pueden seguir el ritmo, hay toda una nueva generación de nuevas empresas que producen vehículos baratos con la capacidad de actualizar o cambiar funciones tan rápido como una actualización de software.

Pero el software tiene limitaciones de velocidad, seguridad y confiabilidad, y muchos fabricantes de automóviles están poniendo sus esfuerzos en poder personalizar el hardware. Aquí es donde encajan los chiplets, y la atención se centra ahora en cómo crear suficiente interoperabilidad en grandes ecosistemas para hacer de este un mercado plug-and-play. Los factores clave para permitir la interoperabilidad de los chiplets automotrices incluyen la estandarización, las tecnologías de interconexión, los protocolos de comunicación, la gestión térmica y de energía, la seguridad, las pruebas y la colaboración del ecosistema.

De manera similar a las aplicaciones no automotrices a nivel de placa, muchos esfuerzos de diseño se centran en un enfoque de matriz a matriz, lo que está impulsando una serie de consideraciones y compensaciones de diseño novedosas. A nivel de chip, las interconexiones entre varios procesadores, chips, memoria y E/S se están volviendo más complejas debido al aumento de los requisitos de rendimiento del diseño, lo que estimula una avalancha de actividades de normalización. Se han propuesto diferentes tipos de interconexión e interfaz para distintos propósitos, mientras surgen chiplet Las tecnologías para funciones dedicadas (procesadores, memorias y E/S, por nombrar algunas) están cambiando el enfoque del diseño de chips.

"Los fabricantes de equipos originales de automóviles se han dado cuenta de que, para controlar su propio destino, tendrán que controlar sus propios SoC", afirmó David Fritz, vicepresidente de sistemas virtuales e híbridos de Siemens EDA. “Sin embargo, no entienden hasta qué punto ha avanzado la EDA desde que estaban en la universidad en 1982. Además, creen que necesitan ir al último nodo de proceso, donde un juego de máscaras costará 100 millones de dólares. No pueden permitírselo. Tampoco tienen acceso al talento porque el grupo de talentos es bastante pequeño. Con todo esto en conjunto, los fabricantes de equipos originales se dan cuenta de que, para controlar su destino, necesitan una tecnología desarrollada por otros, pero que pueda combinarse como sea necesario para tener un producto único y diferenciado que confían en que estará preparado para el futuro al menos para unos pocos. años del modelo. Entonces se vuelve económicamente viable. Lo único que cumple los requisitos son los chiplets”.

Los chiplets se pueden optimizar para funciones específicas, lo que puede ayudar a los fabricantes de automóviles a cumplir con los requisitos de confiabilidad y seguridad con tecnología que ha sido probada en múltiples diseños de vehículos. Además, pueden acortar el tiempo de comercialización y, en última instancia, reducir el costo de diferentes características y funciones.

La demanda de chips ha ido en aumento durante la última década. Según Allied Market Research, la demanda mundial de chips para automóviles crecerá de 49.8 millones de dólares en 2021 a 121.3 millones de dólares en 2031. Ese crecimiento atraerá aún más innovación e inversión en chips para automóviles, y se espera que los chiplets sean un gran beneficiario.

Pero el mercado de chiplets tardará en madurar y probablemente se implementará en fases. Inicialmente, un proveedor proporcionará diferentes tipos de matrices patentadas. Luego, los socios trabajarán juntos para suministrar chips que se apoyen mutuamente, como ya ha sucedido con algunos proveedores. La etapa final serán los chiplets universalmente interoperables, respaldados por UCIe o algún otro esquema de interconexión.

Llegar a la etapa final será lo más difícil y requerirá cambios importantes. Para garantizar la interoperabilidad, deben unirse porciones suficientemente grandes del ecosistema automotriz y la cadena de suministro, incluidos los desarrolladores de hardware y software, fundiciones, OSAT y proveedores de materiales y equipos.

El impulso está creciendo

Lo positivo es que no todo empieza desde cero. A nivel de placa, los módulos y subsistemas siempre han utilizado interfaces integradas de chip a chip, y seguirán haciéndolo. Varios proveedores de chips e IP, incluidos Cadence, Diode, Microchip, NXP, Renesas, Rambus, Infineon, Arm y Synopsys, proporcionan chips de interfaz o IP disponibles en el mercado para crear la interfaz de silicio.

El consorcio Universal Chiplet Interconnect Express (UCIe) es la fuerza impulsora detrás del estándar de interconexión abierta y de principio a fin. El grupo lanzó su última especificación UCIe 1.1 en agosto de 2023. Los miembros de la junta incluyen Alibaba, AMD, Arm, ASE, Google Cloud, Intel, Meta, Microsoft, NVIDIA, Qualcomm y Samsung, entre otros. Los socios de la industria están mostrando un amplio apoyo. También se han propuesto AIB y Bunch of Wires (BoW). Además, Arm acaba de lanzar su propia arquitectura de sistema chiplet, junto con una especificación AMBA actualizada para estandarizar protocolos para chiplets.

“Los chiplets ya están aquí, impulsados por la necesidad”, dijo Arif Khan, director senior del grupo de marketing de productos para propiedad intelectual de diseño en Cadence. “Los crecientes tamaños de procesadores y SoC están alcanzando el límite de la retícula y las deseconomías de escala. Las ganancias incrementales derivadas de los avances en la tecnología de procesos son menores que el aumento del costo por transistor y diseño. Los avances en la tecnología de empaquetado (2.5D/3D) y la estandarización de la interfaz a nivel de matriz a matriz, como UCIe, facilitarán el desarrollo de chiplets”.

Casi todos los chiplets que se utilizan hoy en día son desarrollados internamente por grandes fabricantes de chips como Intel, AMD y Marvell, porque pueden controlar estrictamente las características y el comportamiento de esos chiplets. Pero se está trabajando en todos los niveles para abrir este mercado a más actores. Cuando eso suceda, las empresas más pequeñas podrán comenzar a capitalizar lo que los pioneros de alto perfil han logrado hasta ahora e innovar en torno a esos desarrollos.

"Muchos de nosotros creemos que el sueño de tener una cartera de chips interoperables y listas para usar probablemente tardará años en convertirse en realidad", dijo Guillaume Boillet, director senior de marketing estratégico de Arteris, y agregó que la interoperabilidad surgirá de grupos de socios que están abordando el riesgo de especificaciones incompletas.

Esto también está aumentando el atractivo de los FPGA y eFPGA, que pueden proporcionar un nivel de personalización y actualizaciones para el hardware en el campo. "Los chiplets son algo real", afirmó Geoff Tate, director ejecutivo de Flex Logix. “En este momento, una empresa que construye dos o más chiplets puede operar de manera mucho más económica que una empresa que construye matrices del tamaño de una retícula casi sin rendimiento. La estandarización de los chiplets todavía parece estar lejos. Ni siquiera la UCIe es todavía un estándar fijo. No todos están de acuerdo sobre UCIe, pruebas simples y quién es el dueño del problema cuando el paquete integrado no funciona, etc. Tenemos algunos clientes que usan o están evaluando eFPGA para interfaces donde los estándares cambian como UCIe. Pueden implementar silicio ahora y usar eFPGA para cumplir con los cambios de estándares más adelante”.

También hay otros esfuerzos que respaldan los chiplets, aunque por razones algo diferentes, en particular, el costo creciente del escalamiento de dispositivos y la necesidad de incorporar más funciones en los chips, que están restringidos por la retícula en los nodos más avanzados. Pero esos esfuerzos también allanan el camino para los chiplets en la industria automotriz, y existe un fuerte respaldo de la industria para que todo esto funcione. Por ejemplo, bajo el patrocinio de SEMI, ASME y tres Sociedades IEEE, la nueva Hoja de Ruta de Integración Heterogénea (HIR) analiza diversas cuestiones de diseño, materiales y embalaje de microelectrónica para elaborar una hoja de ruta para la industria de semiconductores. Su enfoque actual incluye 2.5D, 3D-IC, empaquetado a nivel de oblea, fotónica integrada, MEMS y sensores, y sistema en paquete (SiP), aeroespacial, automotriz y más.

En la reciente Cumbre Global de Integración Heterogénea 2023, representantes de AMD, Applied Materials, ASE, Lam Research, MediaTek, Micron, Onto Innovation, TSMCy otros demostraron un fuerte apoyo a los chiplets. Otro grupo que apoya los chiplets es el Intercambio de diseño de chiplet (CDX), que forma parte del grupo de trabajo Arquitectura abierta de dominio específico (ODSA) y la Open Compute Project Foundation (OCP). La carta de Chiplet Design Exchange (CDX) se centra en las diversas características de los chiplets y su integración, incluidos los estándares de intercambio de diseño eléctrico, mecánico y térmico de los circuitos integrados 2.5D apilados y 3D (3D-IC). Entre sus representantes se encuentran Ansys, Applied Materials, Arm, Ayar Labs, Broadcom, Cadence, Intel, Macom, Marvell, Microsemi, NXP, Siemens EDA, Synopsys y otros.

"Las cosas que las empresas automotrices quieren en términos de lo que hace cada chiplet en términos de funcionalidad todavía están en un modo convulso", señaló Fritz de Siemens. “Un extremo tiene estos problemas, el otro extremo tiene esos problemas. Este es el punto ideal. Esto es lo que se necesita. Y estos son los tipos de empresas que pueden salir y hacer ese tipo de trabajo, y luego podrías juntarlas. Entonces esto de la interoperabilidad no es gran cosa. El OEM puede hacerlo demasiado complejo diciendo: "Tengo que manejar todo ese espectro de posibilidades". La alternativa es que podrían decir: "Es como un PCIe de alta velocidad". Si quiero comunicarme de uno a otro, ya sé cómo hacerlo. Tengo controladores que ejecutan mi sistema operativo. Eso resolvería muchísimos problemas y creo que ahí es donde terminará”.

¿Un camino hacia el desarrollo universal de chipsets?

En el futuro, los chiplets son un punto focal tanto para la industria automotriz como para la industria de chips, y eso involucrará todo, desde IP de chiplet hasta interconexiones de memoria y opciones y limitaciones de personalización.

Por ejemplo, Renesas Electronics anunció en noviembre de 2023 planes para sus SoC y MCU de próxima generación. La compañía apunta a todas las aplicaciones principales en el dominio digital automotriz, incluida información avanzada sobre su R-Car SoC de quinta generación para aplicaciones de alto rendimiento con tecnología avanzada de integración de chiplets en el paquete, que están destinadas a brindar a los ingenieros automotrices una mayor flexibilidad para personalizar. sus diseños.

Renesas señaló que si se requiere más rendimiento de la IA en los sistemas avanzados de asistencia al conductor (ADAS), los ingenieros tendrán la capacidad de integrar aceleradores de IA en un solo chip. La compañía dijo que esta hoja de ruta surge después de años de colaboración y discusiones con clientes de Nivel 1 y OEM, que han estado clamando por una forma de acelerar el desarrollo sin comprometer la calidad, incluido el diseño y la verificación del software incluso antes de que el hardware esté disponible.

"Debido a las necesidades cada vez mayores de aumentar la computación bajo demanda y la creciente necesidad de mayores niveles de autonomía en los automóviles del mañana, vemos desafíos en las soluciones monolíticas que escalan y satisfacen las necesidades de rendimiento del mercado en los próximos años", dijo Vasanth Waran, director senior de Estrategias y Negocios de SoC en Renesas. "Los chiplets permiten que las soluciones informáticas escale más allá de las necesidades del mercado".

Renesas anunció planes para crear una familia de productos basados en chiplets dirigido específicamente al mercado de la automoción a partir de 2025.

Las interfaces estándar permiten la personalización del SoC

No está del todo claro cuánta superposición habrá entre los procesadores estándar, que es donde se utilizan la mayoría de los chiplets hoy en día, y los chiplets desarrollados para aplicaciones automotrices. Pero las tecnologías y los desarrollos subyacentes ciertamente se complementarán entre sí a medida que esta tecnología se traslade a nuevos mercados.

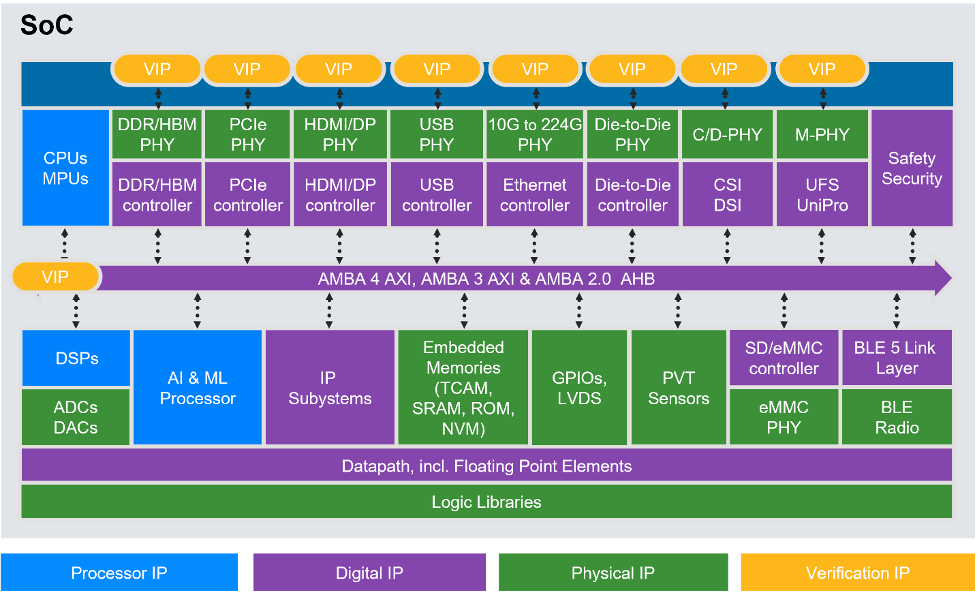

"Ya sea un acelerador de IA o una aplicación automotriz ADAS, los clientes necesitan bloques IP de interfaz estándar", señaló David Ridgeway, gerente senior de productos del grupo de soluciones aceleradas IP de Synopsys. “Es importante proporcionar subsistemas IP completamente verificados en función de sus requisitos de personalización de IP para respaldar los componentes del subsistema utilizados en los SoC de los clientes. Cuando digo personalización, es posible que no se dé cuenta de cuán personalizable se ha vuelto la IP en el transcurso de los últimos 10 a 20 años, tanto en el lado de la PHY como en el del controlador. Por ejemplo, PCI Express pasó de PCIe Gen 3 a Gen 4, a Gen 5 y ahora a Gen 6. El controlador se puede configurar para admitir múltiples modos de bifurcación de anchos de enlace más pequeños, incluidos uno x16, dos x8 o cuatro x4. Nuestro equipo de IP del subsistema trabaja con los clientes para garantizar que se cumplan todos los requisitos de personalización. Para las aplicaciones de IA, la integridad de la señal y la energía es extremadamente importante para cumplir con sus requisitos de rendimiento. Casi todos nuestros clientes buscan ir más allá para lograr las velocidades de ancho de banda de memoria más altas posibles para que su TPU pueda procesar muchas más transacciones por segundo. Siempre que las aplicaciones sean computación en la nube o inteligencia artificial, los clientes quieren la tasa de respuesta más rápida posible”.

Fig 1: Los bloques de IP que incluyen procesador, digital, PHY y verificación ayudan a los desarrolladores a implementar todo el SoC. Fuente: Sinopsis

La optimización de PPA tiene como objetivo final aumentar la eficiencia, y esto hace que los chiplets sean particularmente atractivos en aplicaciones automotrices. Cuando la UCIe madure, se espera que mejore exponencialmente el rendimiento general. Por ejemplo, UCIe puede ofrecer un ancho de banda costero de 28 a 224 GB/s/mm en un paquete estándar y de 165 a 1317 GB/s/mm en un paquete avanzado. Esto representa una mejora del rendimiento de 20 a 100 veces. Reducir la latencia de 20 ns a 2 ns representa una mejora de 10 veces. Otra ventaja es una eficiencia energética aproximadamente 10 veces mayor, de 0.5 pJ/b (paquete estándar) y 0.25 pJ/b (paquete avanzado). La clave es acortar la distancia de la interfaz siempre que sea posible.

Para optimizar los diseños de chiplets, el Consorcio UCIe ofrece algunas sugerencias:

- Consideración cuidadosa de la planificación de las líneas de corte arquitectónicas (es decir, límites de los chiplets), optimizando la potencia, la latencia, el área de silicio y la reutilización de IP. Por ejemplo, personalizar un chiplet que necesita un nodo de proceso de vanguardia y al mismo tiempo reutilizar otros chiplets en nodos más antiguos puede afectar el costo y el tiempo.

- Es necesario planificar las limitaciones del embalaje térmico y mecánico para las envolturas térmicas del paquete, los puntos calientes, la ubicación de los chiplets y el enrutamiento y rupturas de E/S.

- Los nodos de proceso deben seleccionarse cuidadosamente, particularmente en el contexto del esquema de entrega de energía asociado.

- Es necesario desarrollar una estrategia de prueba para chiplets y piezas empaquetadas/ensambladas desde el principio para garantizar que los problemas de silicio se detecten en la fase de prueba a nivel de chiplet y no después de que se ensamblan en un paquete.

Conclusión

La idea de estandarizar las interfaces de matriz a matriz se está popularizando rápidamente, pero el camino para lograrlo requerirá tiempo, esfuerzo y mucha colaboración entre empresas que rara vez hablan entre sí. Para construir un vehículo es necesario que un fabricante de automóviles determine. Construir un vehículo con chiplets requiere un ecosistema completo que incluya a desarrolladores, fundiciones, OSAT y proveedores de materiales y equipos para trabajar juntos.

Los fabricantes de equipos originales de automóviles son expertos en montar sistemas y encontrar formas innovadoras de reducir costes. Pero queda por ver con qué rapidez y eficacia pueden construir y aprovechar un ecosistema de chiplets interoperables para reducir los ciclos de diseño, mejorar la personalización y adaptarse a un mundo en el que la tecnología de punta puede estar obsoleta cuando esté completamente diseñada y probada. y disponible para los consumidores.

— Ann Mutschler contribuyó a este informe.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiengineering.com/why-chiplets-are-so-critical-in-automotive/