Desde hace varios años me encuentro con EDA AMIQ El cofundador Cristian Amitroaie cada pocos meses para discutir el estado de la industria, las tendencias clave en diseño y verificación, y las formas en que ayudan a facilitar y acelerar el desarrollo de chips. Noté una nueva característica interesante mencionada en su último comunicado de prensa, entonces le pedí a Cristian más información. Esto dio lugar a un debate animado e interesante.

La mayoría de los diseñadores e ingenieros de verificación escriben su código en SystemVerilog hoy en día, pero hay excepciones. Algunos aprovechan las herramientas de síntesis de alto nivel (HLS) para diseñar en SystemC u otros lenguajes un poco más abstractos que SystemVerilog. Otros escriben en sus propios idiomas y utilizan herramientas personalizadas para generar los archivos SystemVerilog utilizados para la simulación, verificación formal, síntesis y otros pasos del proceso de desarrollo.

Cristian dijo que ocasionalmente ven un término medio en el que los ingenieros escriben código que es principalmente SystemVerilog pero que también contiene declaraciones de "preprocesador" en lenguajes establecidos como Perl y la biblioteca Jinja2 de Python, o en lenguajes propietarios. Utilizan scripts para procesar estos archivos y generar archivos SystemVerilog puros para el resto del flujo. Le pregunté a Cristian cómo el uso de preprocesadores cambia la forma en que los ingenieros usan un entorno de desarrollo integrado (IDE).

Aprendí que los usuarios de las herramientas de diseño y verificación de AMIQ EDA (DVT) La familia IDE quiere tener acceso a todas sus funciones favoritas incluso al editar archivos con código de preprocesador. El equipo de AMIQ EDA desarrolló heurísticas inteligentes para habilitar capacidades IDE completas al editar dichos archivos, tal como lo hacen con SystemVerilog puro. Estas características incluyen hipervínculos de navegación, autocompletar, detección de errores sobre la marcha, soluciones rápidas, refactorización y todas las funciones avanzadas a las que los usuarios de DVT IDE son adictos.

Esto fue intrigante para mí. Estamos hablando de “comprender” archivos de lenguajes mixtos, algo que en realidad no es algo que cualquier compilador pueda digerir fácilmente. Para asegurarme de que lo hago bien y de que esto es real, Cristian invitó a Zeljko Zurzic, el líder del equipo que coordinó el desarrollo de esta capacidad, para que le explicara cómo funciona. Dijo que todo lo que los usuarios deben hacer es informar a DVT IDE sobre la asignación entre los archivos que contienen declaraciones del preprocesador (“archivo p”) y los archivos generados (“archivo g”).

Esto se hace mediante directivas de compilación dedicadas que admiten varios casos de uso. Por ejemplo, hay una manera de decirle al compilador DVT IDE "busque el archivo p correspondiente a partir del comentario del encabezado del archivo g". Una vez hecho esto, los usuarios simplemente editan sus archivos p como si no tuvieran nada de especial. La compilación incremental sobre la marcha señalará cualquier error de SystemVerilog a medida que escribe, los hipervínculos los llevarán por el código, el autocompletado y la refactorización funcionan bien, pueden solicitar varios diagramas, etc.

Las secciones que contienen código de preprocesador están marcadas distintivamente para que los usuarios sepan que se transformarán en código SystemVerilog. En TVP Eclipse IDE pueden ver cómo se genera el código utilizando la Vista de inspección; en TVP IDE para código VS pueden “visitar” las transformaciones. DVT IDE se puede configurar para ejecutar automáticamente el script de preprocesamiento cada vez que se cambia el código del preprocesador. Los usuarios pueden comparar fácilmente el archivo ap con el archivo g correspondiente si lo desean.

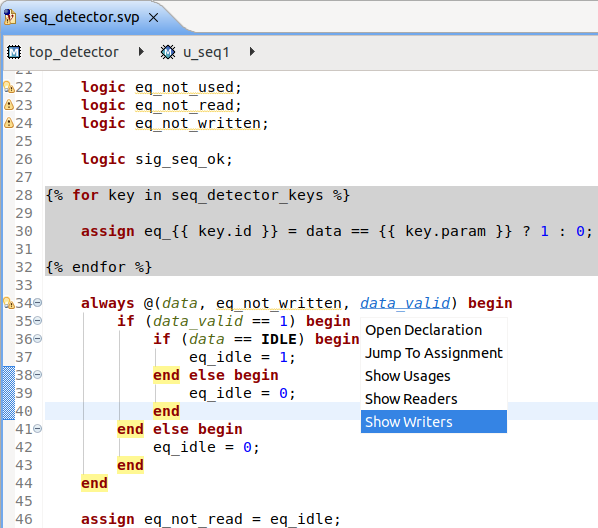

Zeljko proporcionó tres capturas de pantalla que muestran esta nueva capacidad en acción. El primero a continuación muestra un archivo en DVT Eclipse IDE que incluye una declaración de preprocesador Jinja2. A pesar de la presencia de este código que no es de SystemVerilog, el usuario puede aprovechar la potente función "Mostrar escritores" para comprender rápidamente cómo se controla una variable. Los errores y advertencias de compilación se indican en la columna más a la izquierda de la pantalla.

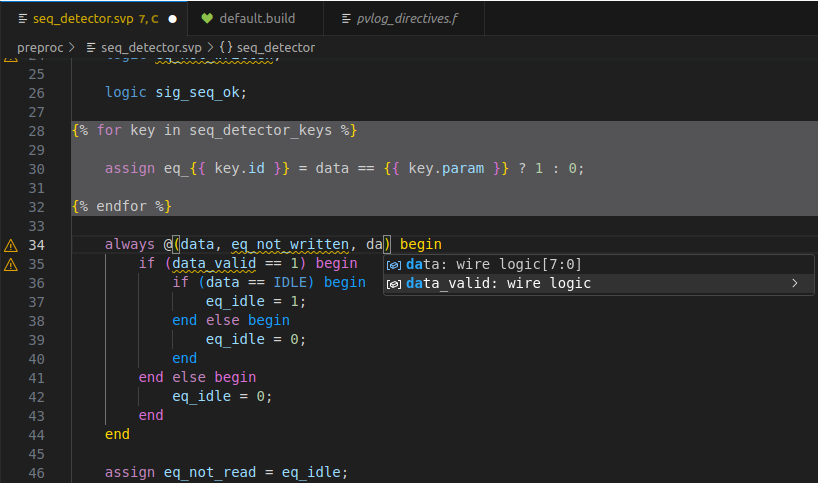

La siguiente captura de pantalla muestra el mismo archivo en DVT IDE para VS Code, mostrando los problemas del compilador en la columna de la izquierda y permitiendo el uso de autocompletar. Esto demuestra cómo incluso las funciones DVT más avanzadas están disponibles en código con declaraciones de preprocesador.

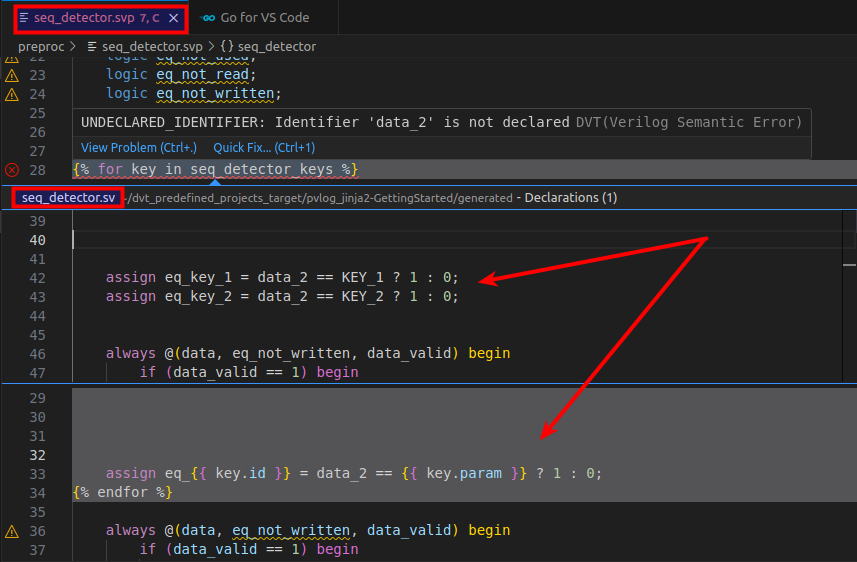

Zeljko enfatizó que el IDE verifica el código SystemVerilog generado, lo cual es importante porque podría haber un error en una declaración del preprocesador o un error en el script de preprocesamiento. La siguiente captura de pantalla muestra un ejemplo de este tipo. El código SystemVerilog generado contiene una variable que no se definió en el archivo fuente. DVT IDE muestra el error de compilación, el archivo p y el código generado en el archivo g.

Ver los archivos g puede ser útil en la depuración, pero la conclusión es que los usuarios trabajan directamente con los archivos p, analizándolos y editándolos utilizando un IDE potente. Los archivos g están etiquetados como "solo lectura" y se advertirá a los usuarios si se modifican. Me alegré de oír esto; Todos sabemos que es una muy mala idea realizar cambios manuales en cualquier archivo que será sobrescrito por un proceso de generación de código.

Finalmente, Cristian enfatizó que el objetivo de esta nueva característica es que los usuarios pueden editar código con declaraciones de preprocesador como si fuera SystemVerilog puro. Hacer esto posible ha supuesto un esfuerzo importante impulsado por unos pocos clientes clave que dependen de flujos basados en preprocesadores. Agradecí a Zeljko y Cristian por sus explicaciones y su tiempo.

Si desea obtener más información sobre el uso de archivos de preprocesador o cualquier aspecto de las soluciones AMIQ EDA, puede visitarlos en el stand 107 en la Conferencia y Exposición de Diseño y Verificación (DVCon) Estados Unidos en San José, California, el 5 y 6 de marzo.

Lea también

Perspectivas 2024 con Cristian Amitroaie, Fundador y CEO de AMIQ EDA

Uso de Linting para escribir código de banco de pruebas sin errores

AMIQ: Celebrando 20 Años en Consultoría y EDA

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/eda/amiq-eda/342053-handling-preprocessed-files-in-a-hardware-ide/