Los crecientes desafíos y el costo creciente del escalamiento lógico, junto con las demandas de un número cada vez mayor de funciones, están empujando a más empresas a adoptar paquetes avanzados. Y si bien eso abre una serie de nuevas opciones, también está provocando una confusión generalizada sobre qué funciona mejor para diferentes procesos y tecnologías.

En esencia, el empaquetado avanzado depende de interconexiones confiables, rutas de señal bien definidas y la minimización de efectos molestos como pérdidas de inserción, diafonía de interconexiones, deformación del sustrato y puntos calientes en el sistema. Esos parámetros pueden variar significativamente dependiendo de la elección del paquete, que puede ser cualquier cosa, desde 2.5D, chip sobre sustrato (FOCoS), 3D-IC o puentes que pueden usarse por separado o junto con otros enfoques. .

Y eso es sólo para empezar. Las hojas de ruta de empaquetado de semiconductores enfatizan interfaces robustas en todo momento, pero no siempre está claro cuál es la adecuada para una aplicación en particular porque hay muchas maneras de llegar a un resultado final. También hay una gran cantidad de procesos nuevos, que incluyen la unión de oblea a oblea, la distribución de energía en la parte trasera y el empaquetado conjunto de ópticas en paquetes. Los intercaladores (puentes) de silicio proporcionan las comunicaciones de mayor ancho de banda, mientras que los intercaladores orgánicos son drásticamente menos costosos y pueden incorporar pasivos a lo largo de la ruta de interconexión desde RDL hasta C4.

Nuevos materiales y arquitecturas.

Desde la invención del primer circuito integrado, los ingenieros han debatido los fundamentos de un material frente a otro. Al principio se trataba de semiconductores de silicio versus semiconductores de germanio, siempre con el objetivo final de fabricar productos electrónicos rentables. La abundancia de silicio y su capacidad para producir un óxido nativo facilitaron la integración y garantizaron la confiabilidad, lo que lo convirtió en el sustrato elegido.

Un avance rápido hasta el día de hoy y la capacidad de fabricación en empaques avanzados está experimentando una metamorfosis similar a la que alguna vez sufrieron los ASIC. En los sectores médico, biotecnológico, HPC, móvil y 5G/6G, los ingenieros están volviendo a los principios físicos y químicos para determinar la mejor manera de combinar la fotónica, la microelectrónica, los puentes de silicio con capas de redistribución y las comunicaciones por chip con la electrónica médica.

El truco consiste en diseñar chips para paquetes utilizando una arquitectura robusta que resista los ciclos de tensión de temperatura y aguante un caso de uso específico.

Al mismo tiempo, los fabricantes de chips están bajo presión para entregar antes módulos a nivel de sistema. Irónicamente, esto requiere en algunos casos procesos de menor temperatura para integrar dispositivos más cerca unos de otros y en lugares nuevos, como el cuerpo humano.

“Hay una cantidad limitada de metales que podemos utilizar para dispositivos implantables, como oro, platino y algunos aceros al cromo. Podemos utilizar óxido de aluminio, pero pocos polímeros son adecuados cuando se exponen a medios orgánicos”, afirmó Dick Otte, director ejecutivo de promex. Los procesos existentes se pueden diseñar para aplicaciones nuevas como dispositivos médicos implantables o probadores de un solo uso para detectar niveles de glucosa o un patógeno como el virus Covid.

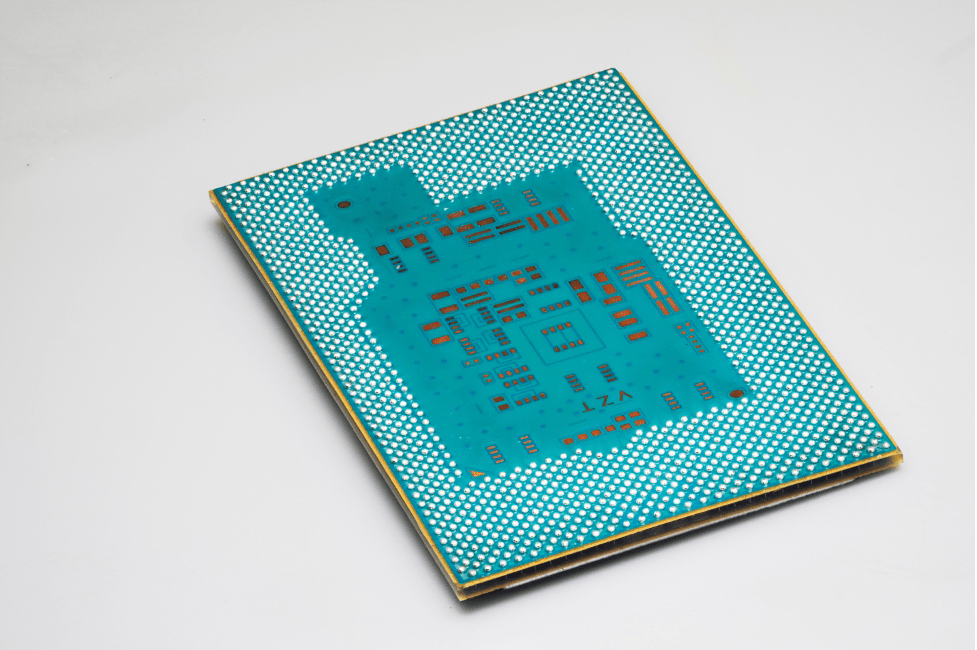

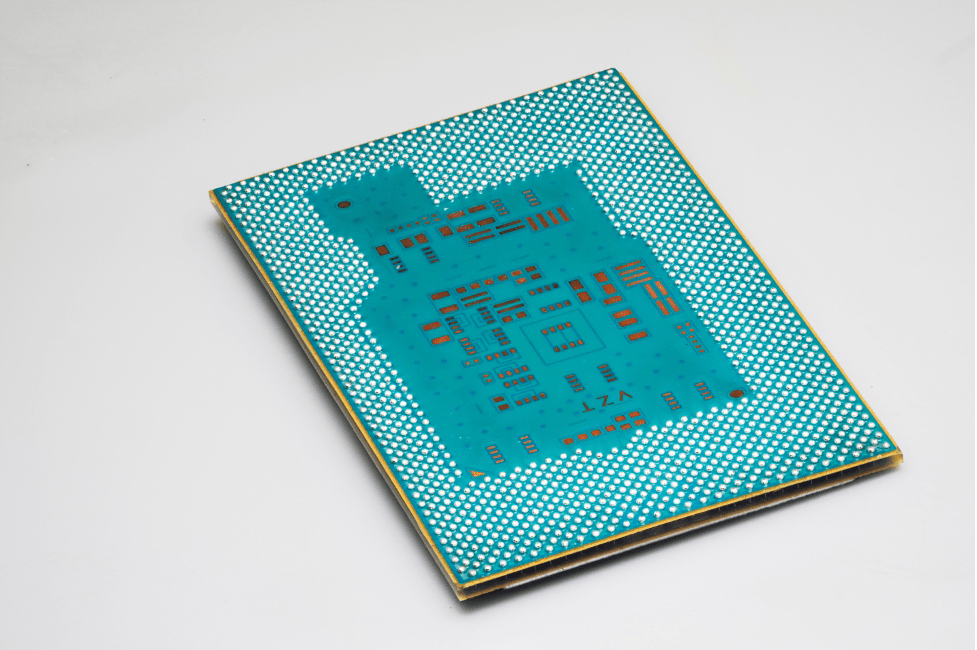

En la informática de alto rendimiento, los problemas que surgen de la deformación y las fluctuaciones de tensión causadas por los ciclos de temperatura están impulsando un cambio total de sustratos orgánicos al vidrio. Intel anunció recientemente prototipos de chips sobre sustrato de vidrio que brindan un camino hacia la ampliación continua de funciones y una mejor entrega de energía en sistemas de alto rendimiento (consulte la figura 1).

Fig. 1: Lado BGA de un chip de prueba de sustrato de vidrio ensamblado. Fuente: Intel

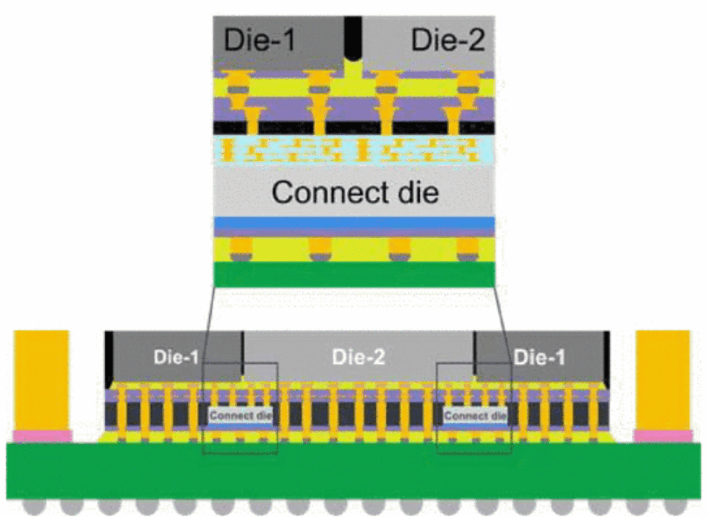

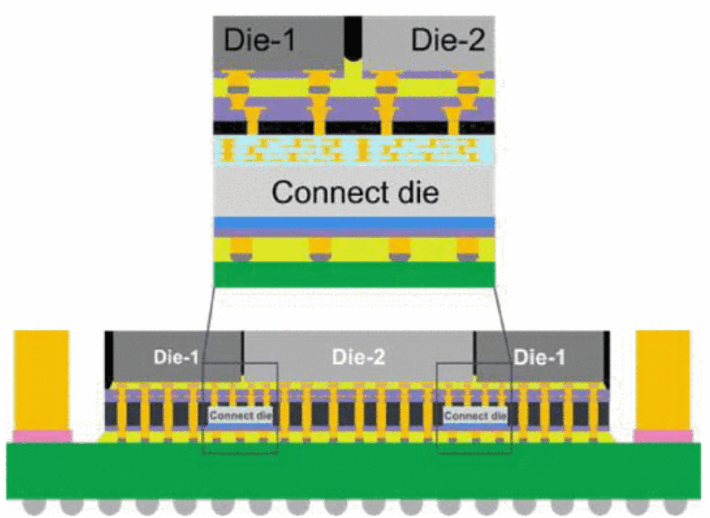

En lugar de sustratos de vidrio rígido, los enfoques de distribución con puentes de silicio están reduciendo la necesidad de costosos sustratos laminados multicapa, que han escaseado en los últimos años. Se puede considerar un puente de silicio como la mejor combinación de los enfoques 2D de lado a lado con chip de despliegue sobre sustrato, FOCoS (ver figura 2).

Fig. 2: Al integrar un puente de silicio de gran ancho de banda (líneas y espacios de 0.5 µm), la deformación del sistema depende del espesor del troquel (450 a 650 µm), el área del molde y el CTE del compuesto de moldeo epoxi. Fuente: Amkor

Los métodos puente ofrecen otros beneficios desde el punto de vista del rendimiento. "En las conexiones puente-matriz, la ruta de la señal se beneficia al tener poca distancia entre las matrices, del orden de 1 a 2 milímetros, por lo que pueden comunicarse bien eléctricamente", dijo Mike Kelly, vicepresidente de Integración y Empaquetado Avanzado en Amkor. "Es un sistema más complicado desde el punto de vista mecánico y de confiabilidad, y podemos tener funcionalidades mixtas como RF y lógica en un paquete".

Cada vez está más claro que los puentes intercaladores de silicio deben ser lo más pequeños posible debido a los costes. Un análisis realizado por los ingenieros de Amkor reveló que las matrices activas más delgadas en la construcción del puente FOCoS son más susceptibles a la deformación. El trabajo también destacó los efectos positivos del uso de masas de moldeo con un coeficiente de expansión térmica (CTE) más bajo como efecto de segundo orden. [1]

Las capas de redistribución con líneas y espacios más amplios (hasta 2 µm L/S) gestionan el segundo nivel de velocidad de interconexión dentro de estos paquetes. En general, la ruta de disipación térmica desde la parte superior de sistemas tan grandes (más allá del tamaño de retícula 3X) requerirá una conductividad aún mayor para eliminar el calor que los materiales de interfaz térmica (TIM) existentes. Con el tiempo, es probable que se necesiten TIM metálicos.

En pocas palabras, los chips lógicos muy espaciados tienden a calentarse como un chip lógico grande en un paquete, con HBM colocado en el perímetro del sistema. Esta es la razón por la que ASE está promoviendo su tecnología de puentes, señalando que el intercalador de silicio (cobre/SiO2) capas del orden de líneas y espacios de 1 µm que tienden a causar mayores pérdidas de inserción y diafonía entre líneas de cobre que en los intercaladores FOCoS, que tienen dimensiones más amplias de cobre y poliimida (3 a 4 µm). Una ventaja clave, además de la comunicación de alta velocidad y gran ancho de banda en los intercaladores de silicio, es la flexibilidad en el enrutamiento del troquel para las trazas de tierra alrededor de las señales de E/S, lo que reduce la diafonía. [2]

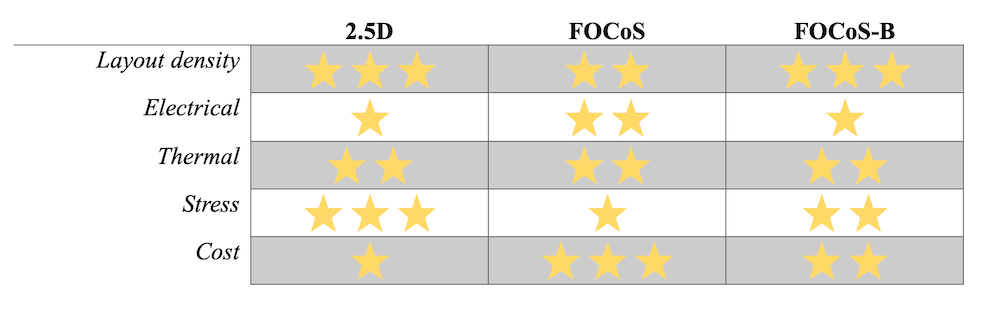

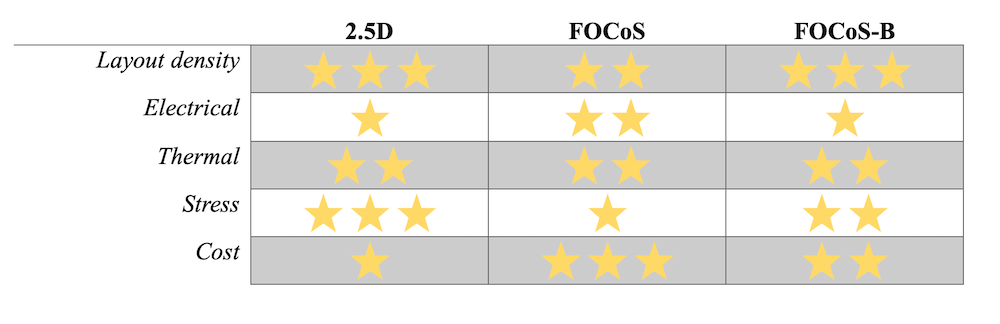

Como resultado, los ingenieros y diseñadores de paquetes tienen opciones dentro de las tecnologías 2.5D, FOCoS y puente FOCoS para sopesar la densidad del diseño, el rendimiento eléctrico/térmico/estrés y el costo según la aplicación específica del módulo (consulte la figura 3), como se resume por ingenieros de ASE. "Se puede esperar que el tamaño de los envases avanzados sea cada vez mayor, y que el comportamiento de deformación y tensión durante el proceso de ensamblaje se vuelva más importante", dijeron.

Fig. 3: Los diferentes atributos de las tecnologías 2.5D, FOCoS y puente. Un puente gestiona las tensiones mejor que FOCoS, pero no tan bien como los enfoques 2.5D. Fuente: ASE

Al mismo tiempo, pronto llegarán ópticas empaquetadas a los centros de datos. Babak Sabi de Intel, vicepresidente senior de desarrollo de tecnología de prueba de ensamblaje en Intel, sostuvo un conector con entradas ópticas en una mesa redonda en el reciente Semicon West. "El empaquetado tiene que ver con interconexiones, y estamos reuniendo muchos núcleos y memoria, y la gente habla de integración de productos a nivel de oblea", dijo. "Aquí es donde el sustrato de vidrio es extremadamente importante, porque podemos eliminar completamente el intercalador".

Además de una hoja de ruta para incorporar sustratos de vidrio para un mejor rendimiento y control de deformaciones a gran escala, Sabi habló sobre la adopción de interconexiones ópticas. "A finales de esta década, comenzaremos a ver dispositivos ópticos en muchos formatos diferentes", dijo, señalando que Intel y sus socios están trabajando en un conector "estándar" para interfaces ópticas con chips. Usó la analogía de una conexión con la que los consumidores están muy familiarizados: USB-C. Para las redes de hiperescala, un conector óptico estándar de la industria puede eliminar las fibras colgantes y los enfoques semiautomáticos de conexión a la fotónica de silicio actual, lo que permite una capacidad de fabricación y automatización superiores.

La necesidad de integrar el procesamiento inicial de obleas con el envasado avanzado también está impulsando cambios en el desarrollo de procesos. Applied Materials presentó recientemente su hoja de ruta para desarrollar conjuntamente herramientas de unión híbrida y colocación de matrices avanzadas de diferentes proveedores con la última plataforma multicámara basada en vacío de Applied. La necesidad de integrar procesos como CMP con vinculación híbrida y herramientas de colocación avanzadas, por ejemplo, está dando lugar a asociaciones entre Applied, EV Group y BESI, y está sucediendo entre otros proveedores y centros de I+D a nivel mundial.

¿Qué tan delgados pueden llegar a ser las obleas y los dispositivos?

Todos estos desarrollos requieren obleas de silicio más delgadas, que a su vez permiten teléfonos móviles, relojes y dispositivos implantables más delgados, entre otras cosas.

Eso también hace que sea más difícil trabajar con ellos y más propensos a variaciones y defectos en el proceso. Pero las obleas deben reducirse para la integración a nivel de dispositivos 3D, y requerirán nuevos tipos de interconexiones, como la unión híbrida, una tecnología en la que Sony fue pionera con sensores de imagen CMOS. En general, las obleas se adelgazan desde aproximadamente 600 a 50 µm o menos.

El progreso desde dispositivos de tamaño milimétrico hasta microLED o microOLED más pequeños que caben en los bordes de las gafas y probadores biotecnológicos desechables también requiere nuevas formas de considerar el ensamblaje. Y si bien parece que los intercaladores de silicio permanecerán seguros en el dominio de las fábricas, los proveedores de OSAT, materiales y equipos están colaborando para ofrecer procesos nuevos o sustancialmente modificados.

"En biotecnología, hay mucha química compleja involucrada porque se utiliza algún tipo de interacción molecular, que la electrónica, la química o los MEMS detectan e intentan igualar, lo que demuestra que un patógeno está presente o no", dijo Otte de Promex. “Entonces, modificamos el proceso de ensamblaje para evitar dañar esas piezas, desarrollando un proceso de curado a temperatura ambiente, por ejemplo”.

Otte explicó que debido a que los dispositivos biotecnológicos interactúan con el paciente y luego envían señales al mundo exterior, no pueden someterse a procesos semiconductores estándar, como el reflujo masivo a 220 °C, la exposición a la luz ultravioleta o la agitación ultrasónica en agua desionizada. El desarrollo de especificaciones en biotecnología o electrónica médica puede tardar dos o más años para cumplir con las especificaciones, y los módulos generalmente requieren estructuras mecánicas (microfluidos) que no pueden exponerse al agua. Estos nuevos requisitos seguirán impulsando nuevos procesos.

Energía trasera, enlaces híbridos y nuevos materiales

Otros cambios también están en marcha. Fundamentalmente, lo que se utiliza se reduce a la física, la química, el rendimiento del dispositivo y el costo, pero eso incluye muchas opciones que pueden adaptarse a una aplicación o caso de uso específico.

La entrega de energía trasera aparecerá primero en los chips de mayor rendimiento. Este enfoque coloca la entrega de energía a los transistores en la parte posterior de la oblea, lo que requiere interconexiones más amplias, mientras que solo las líneas de señal se transportan en la parte frontal de los dispositivos, optimizando el CD para la aplicación. BPD puede mejorar la confiabilidad y al mismo tiempo allanar el camino para integrar dispositivos simples en la parte trasera.

La BPD y los enlaces híbridos son dos de los temas más candentes en la actualidad en semiconductores. Cada uno incluye varios enfoques, y esos enfoques implican diferentes niveles de complejidad. Lo mismo ocurre con los soportes fabricados con obleas de silicio o vidrio, cada uno de los cuales tiene sus ventajas y desventajas. El vidrio, por ejemplo, es muy plano y normalmente se reutiliza en aplicaciones de soporte.

Otro proceso relativamente nuevo es la separación del portador para permitir el procesamiento de obleas delgadas. En un trabajo reciente, imec y Brewer Science revelaron los detalles de un proceso de desunión de soportes de vidrio que se está optimizando para obleas ultrafinas (de 50 µm a 20 µm). [3] En obleas de vidrio de 300 mm, los ingenieros combinaron tres productos químicos, incluido un removedor de cuentas de borde, material de unión temporal y una capa de liberación, que se optimizaron para la liberación limpia de finas obleas de silicio de 300 mm de un soporte mediante un mecanismo de liberación mecánico (cuchilla).

El proceso se optimizó para garantizar la compatibilidad con los óxidos de la parte posterior de la oblea y el procesamiento damasquino dual, evitando al mismo tiempo la pérdida o contaminación involuntaria de la adhesión de la oblea y cumpliendo con las especificaciones de variación del espesor de la oblea (TTV). Permitir la liberación de obleas delgadas es solo uno de los muchos procesos que son importantes para que los enfoques de distribución de energía trasera funcionen.

Conclusión

As OSAT Si adquiere experiencia en la integración de nuevas tecnologías de puentes, el enfoque puede ofrecer beneficios de rendimiento y costos que se encuentran entre los enfoques de integración FOCoS y 2.5D, ampliando las opciones disponibles para los diseñadores. Sin embargo, el uso de estos enfoques de empaquetado de alta densidad todavía está restringido a los fabricantes de chips con niveles internos de integración de oblea a paquete.

Mientras tanto, los ingenieros están ideando soluciones creativas para ensamblar electrónica médica y biotecnológica.

Las empresas están colaborando para unir mejor los mundos de la fabricación de obleas y el ensamblaje y el embalaje. La unión y desunión de obleas y soportes de vidrio probablemente desempeñarán un papel cada vez más importante a medida que los fabricantes de chips sigan combinando capas en dispositivos tridimensionales.

Referencias

- H. Jang et al., “Reliability Performance of S-Connect Module (Bridge Technology) for Heterogeneous Integration Packaging”, 2023 IEEE 73.ª Conferencia de Tecnología y Componentes Electrónicos (ECTC), Orlando, FL, EE. UU., 2023, págs. 1027-1031 , doi: 10.1109/ECTC51909.2023.00175.

- C.-C. Wang et al., “Creative Design and Structure Applied to Chiplets Packaging”, 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, EE. UU., 2023, págs. 1353-1358, doi: 10.1109/ECTC51909.2023.00231.

- K. Kennes et al., “Desafíos del proceso durante la deposición de óxido CVD en la parte posterior de obleas delgadas de 20 μm y 300 mm unidas temporalmente a soportes de vidrio”, 2023 IEEE 73.ª Conferencia de tecnología y componentes electrónicos (ECTC), Orlando, FL, EE. UU. , 2023, págs. 1584-1589, doi: 10.1109/ECTC51909.2023.00269.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiengineering.com/building-better-bridges-in-advanced-packaging/