El futuro de la tecnología de semiconductores a menudo se ve a través de las lentes de los equipos de fotolitografía, que continúan ofreciendo una mejor resolución para los nodos de procesos futuros a pesar de un aluvión casi perpetuo de problemas tecnológicos altamente desafiantes.

Durante años, la litografía se consideró el principal factor de activación relacionado con la fabricación para el escalado continuo del dispositivo, acosado por múltiples retrasos que afectaron el rendimiento en la fábrica que persistió hasta el nodo de proceso de 7 nm. Esos problemas ya se han superado, pero hay una serie de nuevos en el horizonte, así como algunas mejoras importantes.

Expertos de la industria de las comunidades de diseño, fotolitografía, prueba y medición y empaque se reunieron en SEMICON West y DAC de este año para analizar las hojas de ruta de productos para ultravioleta extremo (EUV) y el próximo EUV de alta apertura numérica (high-NA EUV), que incluye los últimos esfuerzos de investigación y desarrollo, así como las barreras para avanzar en la innovación de la litografía y escalar la densidad. Las áreas de discusión incluyeron la mejora de la eficiencia en la energía y el proceso, la mejora de las técnicas de metrología y la exploración de soluciones novedosas como el enmascaramiento curvilíneo y nuevas químicas para fotoprotectores. Sin embargo, en medio de estos avances, se encuentra un enfoque consistente en lograr mayores rendimientos, mayor rendimiento y menor costo por chip.

EUV de alta NA

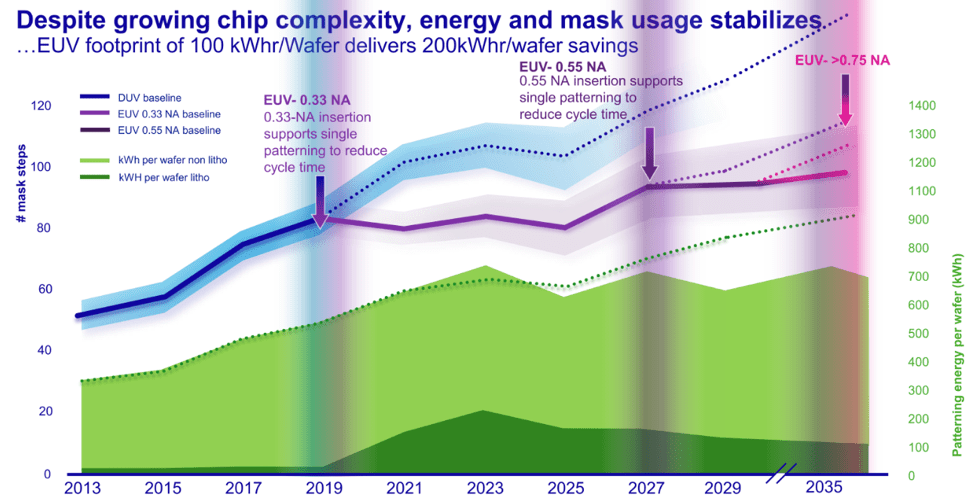

Gran parte de la discusión de este año se centró en lo que sigue para EUV y el cronograma y los requisitos tecnológicos para EUV de alta NA. Michael Lercel, director sénior de marketing estratégico de ASML, dijo que el objetivo es mejorar la eficiencia energética para EUV, así como el estado de desarrollo de sus herramientas EUV de alta NA de próxima generación.

“Las herramientas EUV no son las más eficientes energéticamente, pero estamos haciendo todo lo posible para mejorar la eficiencia energética y la herramienta en sí, de modo que la energía que se necesita para hacer cada oblea mejore significativamente”, dijo Lercel, destacando el papel de apertura numérica (NA) en la evolución de estas herramientas. Si bien el uso general de energía por exposición es mucho mayor que el de la litografía 193i, la capacidad de admitir patrones únicos de dispositivos de mayor densidad significa que se necesitan menos exposiciones. Eso, a su vez, reduce la producción total de energía y el tiempo de ciclo.

High-NA aumenta la apertura numérica de 0.33 a 0.55, mejorando la resolución de un paso de 26 a 30 nanómetros a un paso de 16 nm. Al aumentar la apertura numérica, la resolución mejora, pero la óptica tiene que ser más grande. Eso requiere una máquina más grande, que viene con un beneficio adicional. La herramienta más grande está diseñada para una mejor capacidad de servicio para mantener altos niveles de productividad y mejorar el tiempo de recuperación para volver a la fabricación después del servicio. Los nuevos sistemas de alta NA también son más modulares, lo que facilita que el equipo de servicio reemplace módulos individuales.

Lercel reveló que se construyó el primer sistema completamente ensamblado, pero aún no está operativo ya que no cuenta con la óptica final. Él espera la primera luz sobre estos sistemas a finales de este año.

“Vemos la inserción de 0.55 en los próximos años, y anticipamos que los clientes comenzarán a ponerlos en producción para 2025”, dijo (ver figura 1). “Después de eso, estamos explorando hiper-NA con una apertura numérica de 0.75, que vemos venir en aproximadamente una década.

Fig. 1: ASML espera que 0.55 esté en producción dentro de cuatro años y 0.75 Hyper EUV en aproximadamente una década. Fuente: ASML/SEMICON Oeste

metrología de haz de electrones

Usar un AN más alto para la exposición significa que la luz incide en la oblea en un ángulo más pequeño, conocido como ángulo de incidencia. Como resultado, las estructuras verticales o "relaciones de aspecto" de las características de la oblea se vuelven más difíciles de observar y medir con precisión. Ofer Adan, director sénior de Applied Materials discutió la necesidad de herramientas de metrología más avanzadas para soportar procesos de alto NA. En el nodo de 2 nm y más allá, los defectos se vuelven más difíciles de detectar con las capacidades de imagen de la tecnología de haz de electrones convencional.

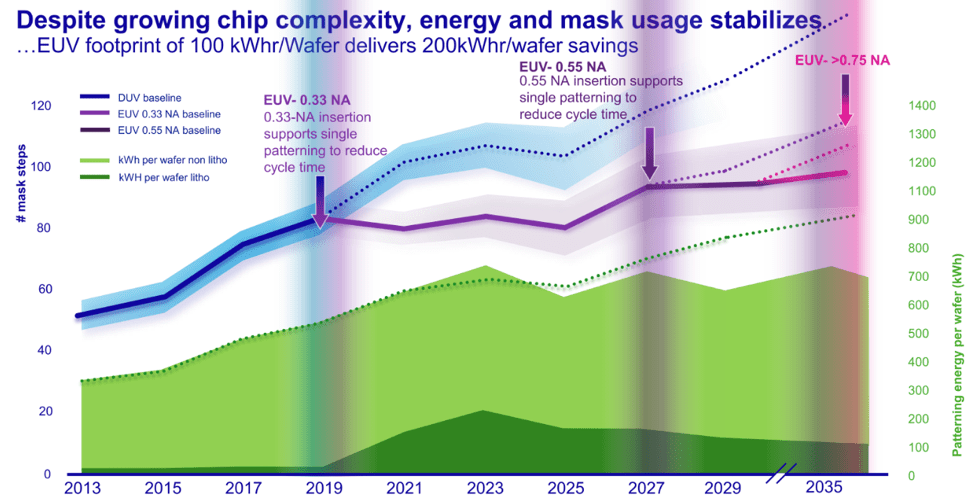

Adan señaló los desarrollos recientes en la tecnología de emisión de campo frío (CFE) como una posible solución para las necesidades de metrología para alta NA. CFE es un tipo de fuente de haz de electrones que funciona a temperaturas más bajas y ofrece varias ventajas sobre las fuentes termoiónicas tradicionales, incluida una resolución espacial mejorada, una mejor estabilidad del haz y una aberración esférica reducida. CFE funciona a temperatura ambiente, lo que da como resultado haces de electrones más estrechos y de mayor energía que producen una resolución más alta y una velocidad de imagen más rápida en comparación con la tecnología de emisión de campo térmico (TFE) convencional (consulte la figura 2). El mayor brillo de esta tecnología ayuda a proporcionar imágenes y mediciones de mayor resolución, pero el tamaño de punto más pequeño significa que el rendimiento se ve significativamente afectado.

“Hay una curva de campo térmico con CFE, que es el equilibrio entre la velocidad de la imagen y la resolución”, dijo Adan. “Puede reducir la resolución y obtener un rendimiento más rápido, o puede mantener la misma velocidad y obtener una resolución más alta. CFE ofrece una velocidad 10 veces más rápida que TFE”.

Fig. 2: CFE ofrece imágenes 10 veces más rápidas con la misma resolución que TFE. Fuente: Materiales Aplicados/SEMICON West.

Hasta hace poco, el uso de CFE se limitaba a entornos de laboratorio porque la estabilidad de la columna de haz de electrones era insuficiente para los estrictos requisitos de la fabricación de semiconductores de gran volumen. Adan mencionó dos innovaciones que han resuelto el desafío de la estabilidad. Uno, un vacío ultraalto extremo dentro de la columna, y el segundo es un proceso de autolimpieza cíclico que elimina continuamente los contaminantes de la fuente de CFE, lo que permite un rendimiento estable y repetible.

Nuevas tecnologías de proceso para alta NA

Angélique Raley, directora de la unidad comercial de grabado de TEL, señaló dos tendencias importantes que dan forma al futuro de EUV. El primero es el cambio de estructuras 2D a 3D, específicamente la transición de finFET a dispositivos gate-all-around (GAA), que impacta significativamente los procesos requeridos en la fabricación de chips. El segundo gira en torno a la escala crítica continua de EUV, especialmente en lo que se refiere a la reducción del paso del metal a tan solo 12 nm.

“A medida que pasamos de GAA a FET de canal de pila (CFET), nos enfrentamos a requisitos de relación de aspecto aún más altos”, dijo Raley. "Este desarrollo vuelve a subrayar la importancia de los procesos de grabado isotrópico y direccional altamente controlables".

Los dispositivos gate-all-around (GAA) se definirán por deposición epitaxial (epi) que implica múltiples capas, lo que exige un control impecable de este proceso de deposición. Los fabricantes de semiconductores deberán idear grabados isotrópicos altamente controlados que puedan grabar materiales simultáneamente en todas las direcciones con selectividad.

El grabado con plasma seguirá siendo indispensable, en particular para los grabados con alta relación de aspecto. Por ejemplo, el grabado por contacto es un proceso complejo de grabado con óxido que exige un alto grado de control.

Con la introducción de EUV de alta NA, los fabricantes tendrán que decidir si utilizar una resistencia amplificada químicamente o una resistencia a base de óxido de metal. Esta transición, junto con una profundidad de enfoque reducida, requerirá un protector más delgado y, por lo tanto, un control de proceso altamente preciso para el grabado. Una resistencia más delgada también significa un uso más extenso de máscaras duras, porque la propia fotoprotección se erosiona más rápidamente en las químicas de grabado.

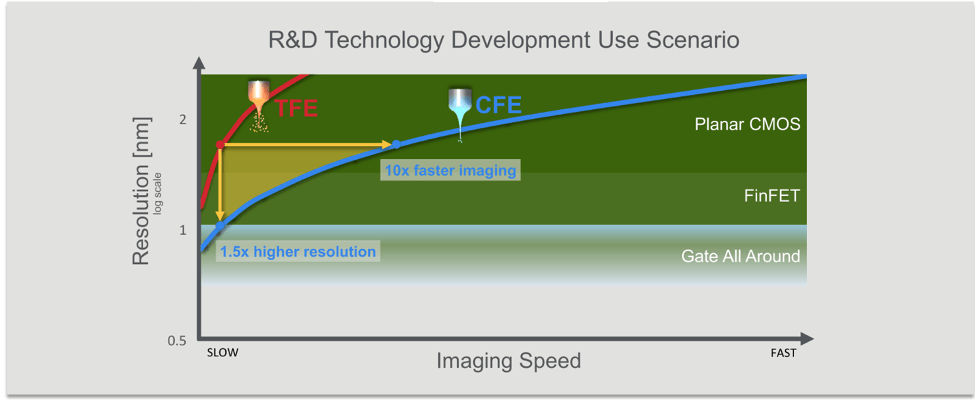

Resistencia seca

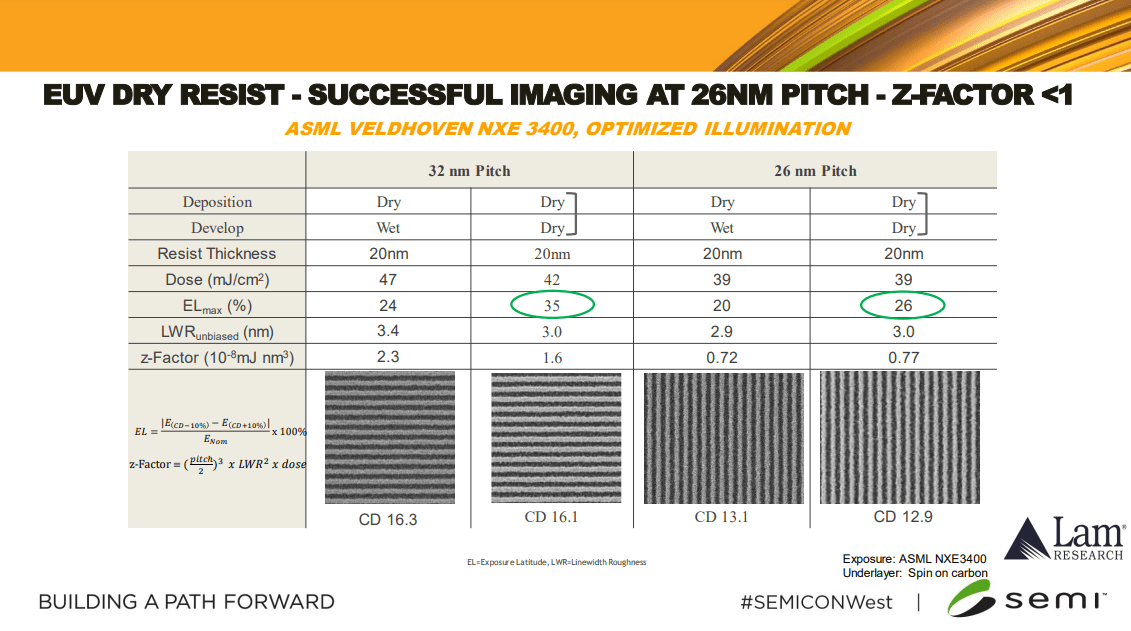

Una solución al problema de la resistencia con NA alta es la resistencia seca. En comparación con el proceso de fotorresistencia amplificado químicamente (CAR, por sus siglas en inglés) convencional, la resistencia seca utiliza un proceso de precursor de gas, que involucra material de resistencia seca y un proceso de revelado en seco, dijo Benjamin Eynon, director senior de marketing de resistencia seca EUV en Investigación de lam. Su tamaño molecular es seis veces más pequeño que CAR, lo que permite imprimir detalles mucho más finos (ver figura 3). También simplifica el proceso al eliminar líquido, lo que reduce el potencial de colapso del patrón. Eynon señaló que Dry Resist también ofrece una reducción de 5X a 10X en los desechos, lo que la convierte en una opción más ecológica.

Fig. 3: Las imágenes de fotorresistencia seca pueden crear patrones de líneas y espacios de 16 nm y 13 nm con una rugosidad de ancho de línea de 3 nm. Fuente: Lam Research/SEMICON West

“Dry resist produce estructuras más consistentes y predecibles con menos desperdicio”, dijo Eynon. “También tenemos una ventaja de resolución para NA alta, donde CAR está luchando por debajo del tono de 35 nm, y estamos viendo mejores resultados muy por debajo de eso”.

Explicó que hacer cambios en el grosor de la resistencia es mucho más simple con la resistencia seca que con el CAR tradicional. “En el pasado, si tenía que pedirle al proveedor de resistencia una resistencia que gira más delgada, tenía que esperar seis meses para todas las pruebas. Ahora podemos simplemente cambiar la receta y dejarla”.

Dry resist ofrece ventajas en términos de ventana de procesamiento y defectos, que son insignificantes, pero todavía hay barreras que superar. La reducción de la dosis para NA alta puede conducir a una mayor rugosidad, por lo que se necesita hacer más trabajo para equilibrar la reducción de la dosis con otros factores como la rugosidad del ancho de línea (LWR).

Steven Sheer, vicepresidente senior de patrones, procesos y materiales avanzados en imec, también destacó las ventajas de la resistencia seca sobre las limitaciones de CAR para la obtención de imágenes lineales y espaciales en los tonos más pequeños que ofrece la NA alta. Pero agregó que se requiere más investigación para reducir la dosis y mejorar la deficiencia. La dosis más baja en los escáneres EUV se correlaciona con un mayor rendimiento.

Imec actualmente está construyendo un laboratorio de alta NA y una línea piloto en Lovaina, Bélgica, en el campus de ASML. Está previsto que se abra en la primera mitad de 2024 para investigar, probar y desarrollar de forma cooperativa las herramientas y los procesos para la litografía EUV de alta NA.

"La EUV de alta NA es más una evolución que una revolución", dijo Sheer. “Tenemos que comprimir la escala de tiempo para producir estas nuevas tecnologías en aproximadamente dos años”. Sheer anticipa que el punto de inserción ideal para NA alta será el nodo de 14 angstrom (1.4 nm).

Otro desafío con EUV de alta NA involucra la metrología, particularmente en lo que respecta a la obtención de imágenes de materiales muy delgados. Sheer citó las dificultades para medir el retorno de la señal débil en los SEM de CD. Se sugirieron como posibles soluciones la optimización de la energía de aterrizaje, diferentes materiales y algoritmos de aprendizaje automático para la eliminación de ruido, la extracción de contraste o la clasificación automática de defectos.

La innovación de máscaras es otra área clave que Sheer ve como un proceso evolutivo para EUV de alta NA.

“En términos de máscaras e imágenes, una de las cosas clave que es importante es que exploramos máscaras de baja n para mejorar el contraste general”, dijo Sheer. “Cuando empiezas a llegar a un tono de 24 nanómetros o menos, empiezas a perder contraste a menos que realmente hayas implementado las máscaras low-n. Así que creemos que esta es una tecnología importante que debe desarrollarse”.

Máscaras curvilíneas para un diseño con curvas

Durante tres décadas, la tecnología de máscaras de semiconductores se mantuvo prácticamente sin cambios, y la creación de máscaras se llevó a cabo en máquinas de modelado variable que restringían los elementos variables a un ángulo de 45 grados. A medida que las características se reducían y se volvían más complejas, los escritores de máscaras e-beam y multihaz ofrecían flexibilidad en el diseño. Ahora, prácticamente el 100 % de las máscaras se fabrican con tecnología multihaz, lo que presenta nuevas oportunidades para diseños más complejos y eficientes en sistemas de NA alta.

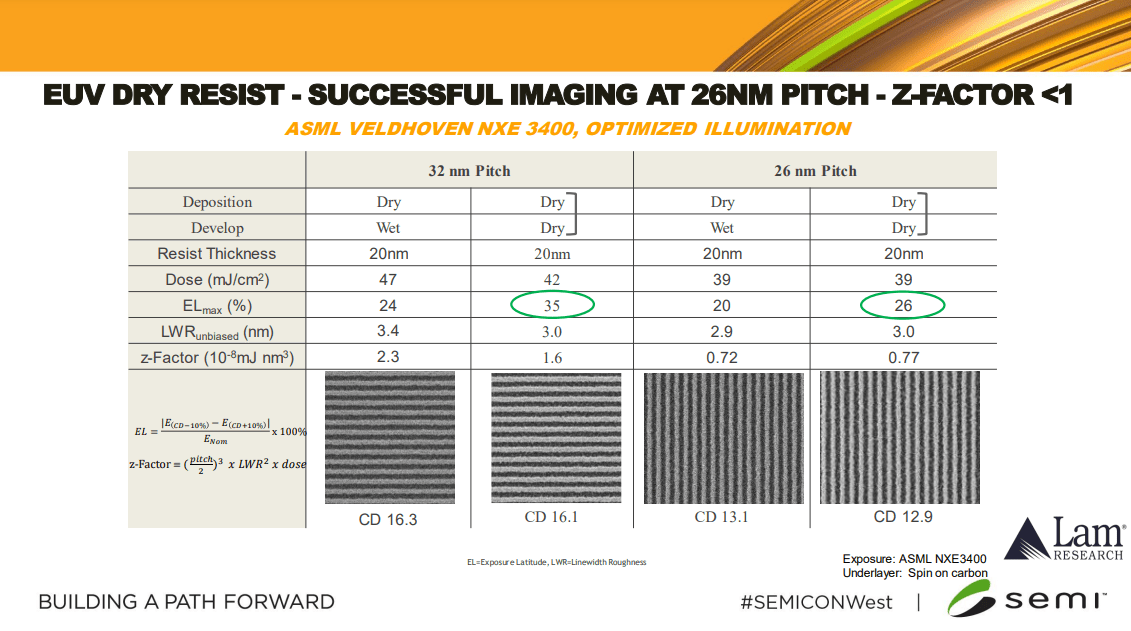

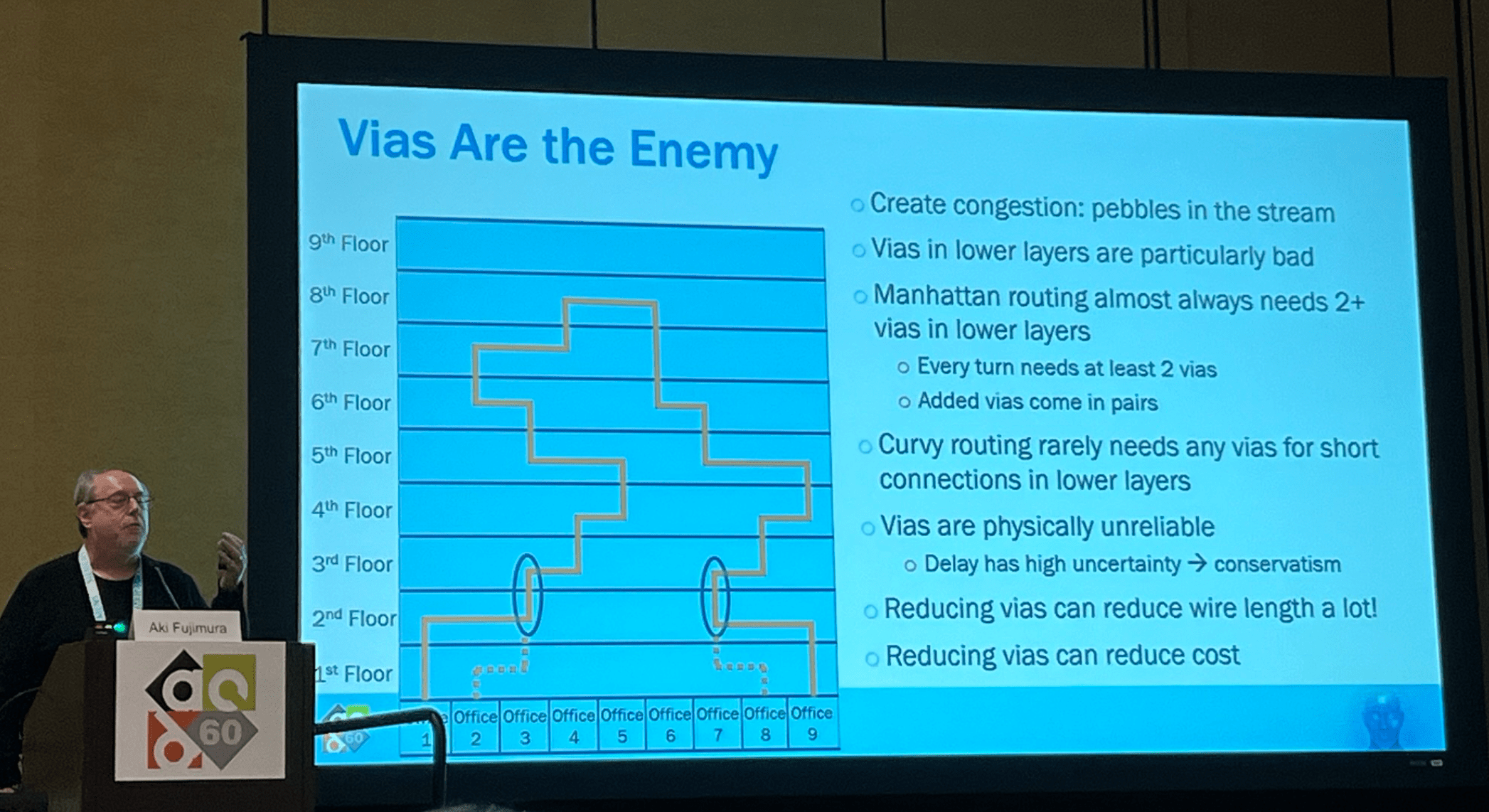

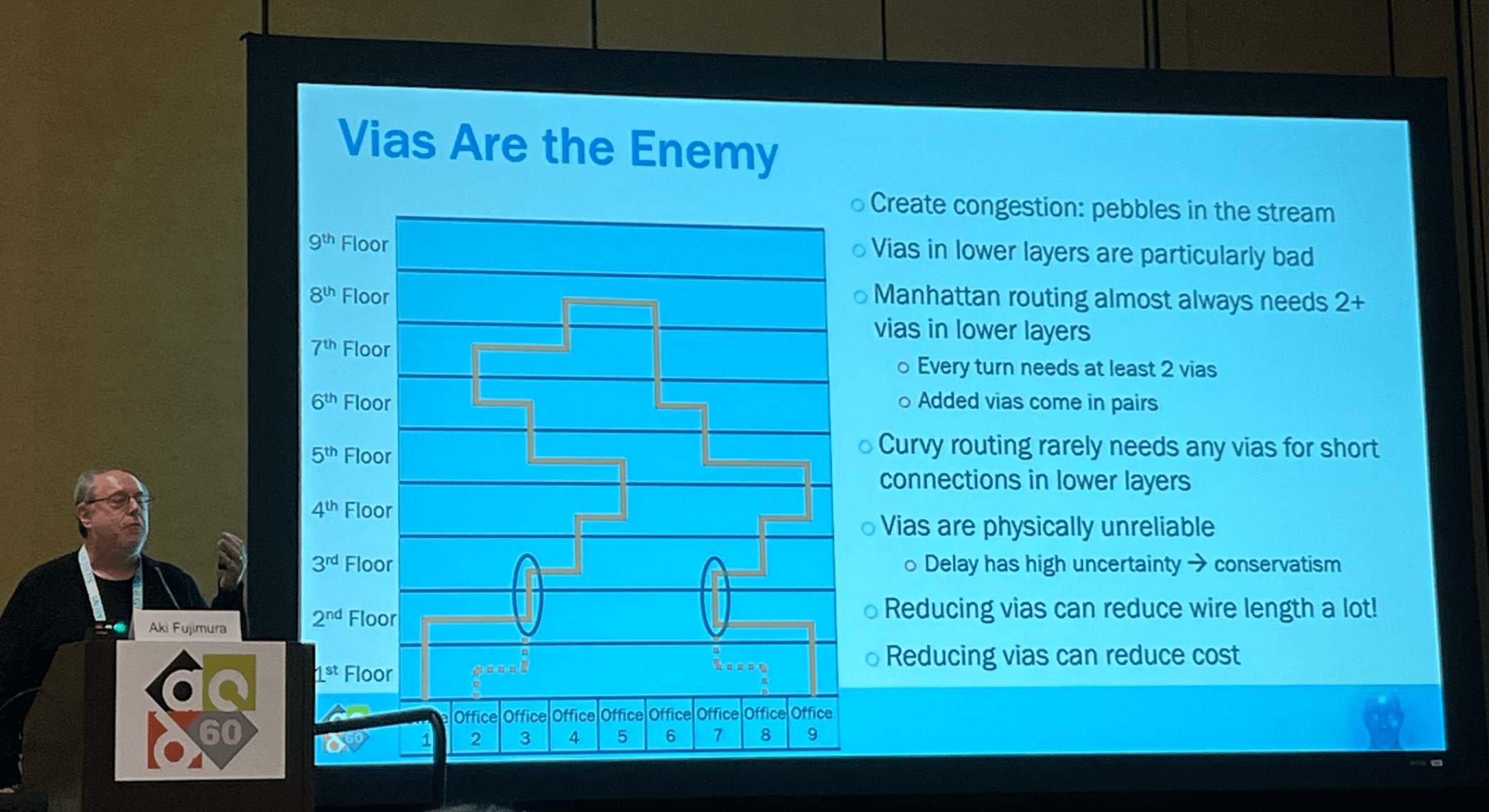

En una presentación de panel en DAC, Aki Fujimura, CEO de D2S, discutió el surgimiento de la fabricación curvilínea que es posible ahora y ganó interés por su potencial para aumentar el rendimiento, reducir el tamaño del chip, usar menos energía y mejorar el rendimiento y la confiabilidad.

“Cualquier forma ahora se puede proyectar con la misma precisión en la misma cantidad de tiempo”, dijo Fujimura. “La vida útil de las máscaras ya no depende del tipo de forma que esté tratando de presentar y, por lo tanto, el costo de la máscara es constante, independientemente de la forma que esté proyectando”.

Un objetivo clave de EUV de alta NA es reducir la complejidad y reducir el tiempo de respuesta general y el costo de la fabricación de obleas, y las máscaras curvilíneas prometen una mejora significativa en esas áreas.

Steve Teig, director ejecutivo de Perceive, demostró cómo el diseño con curvas puede reducir la cantidad de vías en un diseño de chip hasta en un 50 %, reducir el cableado en un 30 % y reducir los costos de fabricación hasta en un 30 % (consulte la figura 4). “Reducir la cantidad de vías puede reducir la longitud del cable mucho más de lo que piensa”, dijo. “Es posible reducir enormemente el número de vías y hacer chips mucho más pequeños, mucho más rápidos, mucho menos costosos y con muchas menos capas. Esta es la promesa del enrutamiento con curvas”.

Fig. 4: Teig de Perceive explica por qué las vías no son su amigo, en el Curvy Design Panel, DAC 2023. Fuente: Semiconductor Engineering / Susan Rambo

Los diseños curvilíneos también resuelven muchos problemas estocásticos en los nodos inferiores. Teig comparó los procesos de litografía actuales con disparar un arco y una flecha a un objetivo y apuntar al borde exterior en lugar de a la diana. “Si está imprimiendo un alambre en forma de salchicha en lugar de uno cuadrado, puede apuntar al centro, y los problemas estocásticos y de aspereza en el borde de la línea se vuelven mucho menos problemáticos”, dijo.

La variación plantea otro desafío. “Es imposible producir esquinas de noventa grados en una oblea”, agregó Fujimura. “Lo sabemos, pero ese es el diseño que tenemos, así que tratamos de acercarnos lo más posible. Y lo más importante en la fabricación es la variación, no solo que desee hacerlo bien, en promedio, sino que desee que la desviación estándar del promedio sea lo más pequeña posible”.

John Kibarian, presidente y director ejecutivo de Soluciones PDF, destacó que el diseño curvilíneo promete un futuro innovador, especialmente en el ámbito de la integración, desde el diseño de sistemas hasta el reordenamiento de átomos. Sus ventajas únicas, como la reducción de la altura de la pista mientras se mantiene la porosidad y la estabilidad, son cruciales para escalar en el futuro.

Sin embargo, el cambio hacia la fabricación curvilínea no está exento de desafíos. La adopción generalizada de este enfoque de diseño innovador requiere cambios significativos en el software de automatización de diseño electrónico (EDA), la dinámica organizacional y los protocolos de prueba y medición. Sin embargo, estos obstáculos se ven superados con creces por la promesa de mayor rendimiento, menor tamaño de chip, menor consumo de energía y mayor rendimiento y confiabilidad que ofrece el diseño curvilíneo a la fabricación de semiconductores.

“El futuro será mucho más acerca de la innovación como integradores”, dijo Kibarian. “Si observa lo que nuestra industria dice que implicará la próxima década, se trata de la integración hacia arriba y hacia abajo desde el diseño del sistema hasta la litografía, la metrología y los nuevos materiales que permiten mejoras en los procesos. Cualquier cosa que le permita reducir el tamaño, reducir la energía y reducir los costos mientras mantiene la estabilidad se integrará en el proceso, y ese es uno de los mayores beneficios potenciales para el diseño con curvas”.

Conclusión

La evolución de la fotolitografía es una piedra angular para el escalado de semiconductores, lo que permite la miniaturización continua de patrones de circuitos y el correspondiente aumento en la densidad y el rendimiento de los circuitos. El futuro de la litografía parece prometedor con la introducción de herramientas EUV más eficientes desde el punto de vista energético, la evolución de herramientas de alta apertura numérica y el enfoque holísticamente integrado de las innovaciones para mejorar la resolución y controlar las dimensiones.

Si bien la industria actual ha logrado cierto éxito en la integración de nuevos materiales en el ecosistema, la reducción del tamaño del campo que ofrecen los dispositivos de alta NA presenta nuevos desafíos para las resistencias, la metrología, la fabricación de máscaras y el control de procesos. Sin embargo, si los últimos 40 años han demostrado algo, es que la industria siempre encuentra el camino a seguir.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Automoción / vehículos eléctricos, Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- Desplazamientos de bloque. Modernización de la propiedad de compensaciones ambientales. Accede Aquí.

- Fuente: https://semiengineering.com/high-na-lithography-starting-to-take-shape/