El 13 de septiembre de 2021, Andes Technology Corporation emitió con éxito su oferta pública GDR (Global Depositary Receipt) en la Bolsa de Valores de Luxemburgo. En ese momento, convirtió a Andes en el único proveedor internacional público de IP de CPU con arquitectura de conjunto de instrucciones (ISA) RISC-V. Esto permitió a inversores de todo el mundo participar en el crecimiento que Andes imaginaba para RISC-V. Esta inyección de capital impulsaría la ambición de Andes de convertirse en líder en el mercado RISC-V de estándar abierto, de alto crecimiento y en rápida evolución. En 2015, reconociendo el gran potencial de RISC-V ISA, Andes se convirtió en miembro fundador y principal de RISC-V International.

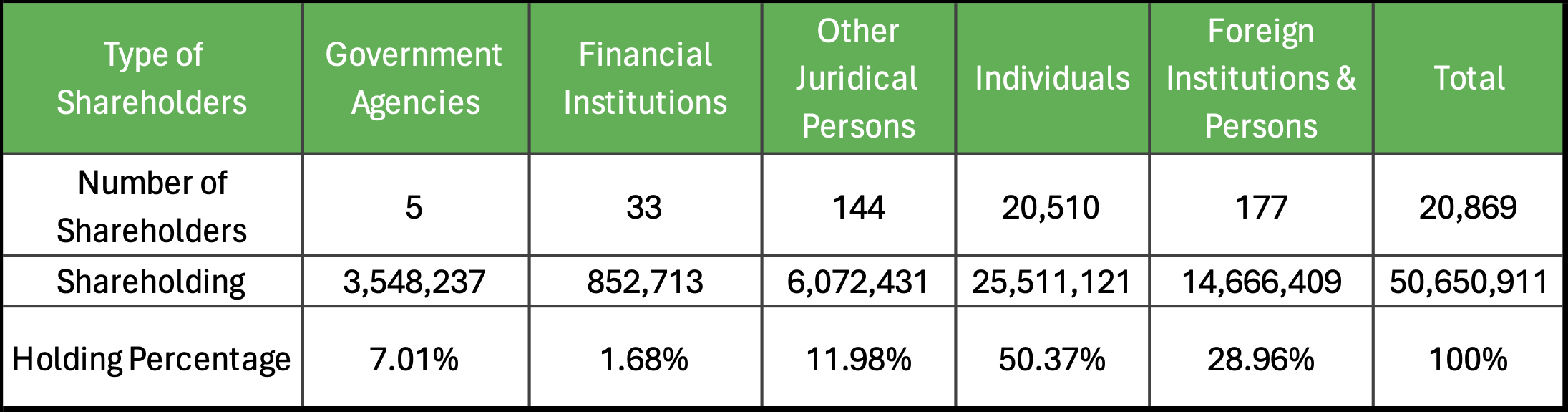

Al 2 de abril de 2023; Unidad: Acciones, %

La inversión ha dado sus frutos de manera significativa, particularmente porque coincidió con la ratificación de la extensión vectorial RISC-V en noviembre de 2021. Este evento marcó un punto de inflexión en la evolución de la arquitectura del conjunto de instrucciones RISC-V. La extensión vectorial RISC-V llegó en un momento en que la informática del centro de datos estaba cambiando del procesamiento de propósito general al procesamiento de IA, que maneja conjuntos de datos extremadamente grandes. El procesamiento vectorial sobresale en el procesamiento eficiente de grandes matrices o datos estructurados. El procesamiento de vectores tiene el potencial de convertir a RISC-V en el próximo ISA importante a nivel mundial.

La arquitectura altamente paralela de un procesador vectorial reduce la latencia y la sobrecarga. Logra una mejor eficiencia energética al maximizar la utilización de recursos de la CPU y minimizar los ciclos inactivos, logrando así un mayor rendimiento por vatio. Además, el hardware para implementar unidades de procesamiento vectorial (VPU) y registros vectoriales RISC-V es más simple que las arquitecturas altamente paralelas utilizadas para el procesamiento de gráficos. Y las VPU proporcionan un modelo de programación mucho menos complejo.

Los equipos de I+D de Andes, tanto en la operación de América del Norte como en el personal ampliado de Taiwán, se han centrado en desarrollar arquitecturas de vanguardia para procesadores RISC-V de alta gama. En particular, los dos lograron un hito importante al desarrollar el primer motor vectorial RISC-V (RVV), el AndesCore™ NX27V, basado en la especificación RVV internacional RISC-V. Mostrando la agilidad y la innovación del equipo de ingeniería de Andes, el diseño se completó en un año y se basó en la versión V0.8 de la especificación de extensión vectorial RISC-V, y luego se modificó a la versión V1.0 cuando se ratificó RVV. Este logro condujo a algunas victorias importantes en el diseño de OEM.

El año pasado, en la conferencia del Simposio Internacional sobre Arquitectura de Computadoras (ISCA) 2023 en Orlando, Florida, META presentó su artículo, “MTIA: First Generation Silicon Targeting Meta's Recommendation Systems”, que es el proyecto de servidores de IA del centro de datos de la compañía. Hay 64 elementos de procesamiento (PE) en el diseño del servidor que admiten el acelerador propietario personalizado de MRETA. Cada PE contiene dos procesadores: uno escalar y otro vectorial. Ambos son IP de Andes que los ingenieros de META personalizaron altamente, utilizando Andes Custom Extensions (ACE) para producir una solución completamente única dirigida a los requisitos informáticos de IA específicos de META.

El diseño validó la eficacia de RISC-V con Vector Extensions como una poderosa solución para las necesidades informáticas de los centros de datos de IA en un momento en que la demanda de hardware de procesamiento de centros de datos está aumentando. De acuerdo a Perspectivas del mercado futuro' informe “Perspectivas del mercado de CPU para centros de datos (2023 a 2033)”, Se espera que el mercado de CPU para centros de datos crezca significativamente en los próximos años, impulsado por la creciente demanda de computación en la nube, análisis de big data e inteligencia artificial (IA). . Los factores clave de este crecimiento incluyen la necesidad de un procesamiento de datos más rápido, una mayor eficiencia y costos reducidos.

En 2021, además de las extensiones de vectores, RISC-V International ratificó 11 extensiones más. La Figura 1 ilustra la hoja de ruta del producto Andes para respaldar estas extensiones. En el camino hacia finales de 2022, desde entonces se entregaron las series N25F-SE, 27 y 45; en 2023, Andes entregó al mercado seis nuevos núcleos RISC-V, como D25F-SE, D23, N225, NX45V, AX45MPV. así como AX65. La hoja de ruta abarca desde el procesador RISC-V básico de bajo consumo y alta seguridad AndesCore™ D23 hasta el AX65, el primero de la serie 60, que se lanzó en el cuarto trimestre de 2023 y ahora se envía para diseños de clientes.

El AX65 es un procesador fuera de orden de 13 etapas, 4 vías, 64 bits con perfil RVA 22 (el perfil RVA22U64 especifica las funciones ISA disponibles para entornos de ejecución en modo de usuario en procesadores de aplicaciones de 64 bits). Equipada con un proceso de 13 etapas, decodificación de 4 anchos y ejecución fuera de orden de 8 anchos, la serie está dirigida a los zócalos de procesadores de aplicaciones Linux de informática, redes y controladores de alta gama.

El AX65 permite clústeres multinúcleo de uno a cuatro a ocho núcleos. El rendimiento es de clase mundial, operando a una frecuencia de reloj de 2.4 gigahercios en un proceso TSMC de siete nanómetros. El rendimiento de los números enteros de especificación (Specint 2006) es de 8.25 por gigahercios, y un SpecFp2006 es de 10.2 por gigahercios, que son el rendimiento de SPEC CPU® 2006 más conocido con diseño de caché de dos niveles. Los modelos AX66, AX63 y AX67 se entregarán posteriormente.

Otra área en la que Andes ha realizado una inversión significativa es la CPU IP RISC-V de alto rendimiento para automóviles. Se prevé que la penetración de SoC RISC-V en diseños automotrices alcance el 21.4% para 2030, según The SHD Group. "Informe de mercado RISC-V: pronósticos de aplicaciones en un mundo heterogéneo". Andes desarrolló productos funcionales compatibles con la seguridad, entre los que se incluyen su N25F-SE, la primera CPU IP RISC-V del mundo totalmente compatible con ISO 26262; D25F-SE, que admite instrucciones de extensión DSP; y los procesadores de la serie 45-SE que cumplen con el nivel ASIL más alto, ASIL D. La función ACE se mejorará para agregar soporte para los procesadores de la serie 45.

Gracias a la demanda que han experimentado los productos Andes RISC-V, la empresa sigue siendo rentable y sigue disfrutando de un rápido crecimiento. De 2021 a 2023, los ingresos de Andes mostraron un crecimiento de casi el 30%. Esto fue impulsado por más de 300 licenciatarios comerciales y más de 600 acuerdos de licencia firmados con clientes distribuidos geográficamente en Taiwán, China, Corea, Japón, Europa y Estados Unidos. La plantilla mundial de la empresa creció casi un 70% durante el mismo período.

Conclusión

En una era definida por la rápida evolución tecnológica, Andes Technology Corp. se encuentra a la vanguardia de la innovación en el mercado IP de CPU RISC-V. Desde su emisión pionera de recibos de depósito en el extranjero (GDR) hasta sus avances innovadores en la arquitectura RISC-V, Andes Technology continúa redefiniendo los estándares de la industria y dando forma al futuro de la informática. A medida que la demanda de soluciones informáticas eficientes y de alto rendimiento continúa aumentando, Andes Technology mantiene su compromiso de ofrecer soluciones RISC-V incomparables para impulsar un cambio transformador en todo el panorama tecnológico global.

Lea también

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/ip/343097-andes-technology-pioneering-the-future-of-risc-v-cpu-ip/