Escuché por primera vez sobre la síntesis de alto nivel (HLS) mientras trabajaba en EDA en Viewlogic en la década de 1990, y he seguido las tendencias en las últimas décadas. A principios de este año, Siemens EDA organizó un evento de dos días en el que oradores de empresas conocidas compartieron sus experiencias sobre el uso de HLS y Verificación de alto nivel (HLV) en sus productos semiconductores. Recapitularé los puntos principales de cada orador en este blog.

stuart clubb de Siemens EDA dio inicio al evento de dos días, y explicó cómo las CPU de uso general han tenido problemas para satisfacer las demandas informáticas, la productividad del diseño RTL se está estancando y que los costos de verificación de RTL solo están aumentando. HLS ayuda al reducir los tiempos de simulación y verificación, lo que permite una mayor exploración arquitectónica y permite que los nuevos procesadores y aceleradores específicos de dominio manejen nuevas cargas de trabajo de manera más eficiente. La herramienta de Siemens EDA para HLS y HLV se llama Catapultar.

Catapultar

Con la herramienta Catapult, los diseñadores modelan a un nivel más alto que RTL con C++, SystemC o MatchLib, que luego produce código RTL para herramientas de síntesis lógica tradicionales. Su código fuente HLS se puede orientar a un ASIC, FPGA o incluso eFPGA. Incluso hay un flujo de análisis de energía compatible con el PowerPro Añadir.

NXP

Esta empresa tiene 31,000 11.06 personas, produciendo ingresos de $2021 30 millones en 11, ubicadas en 802.15.4 países y Reinhold Schmidt habló sobre su grupo de 33 ingenieros de acceso seguro para automóviles. Su producto incluía un transceptor IR-UWB compatible con IEEE 40z, ARM Cortex M28 y un DSP; Comenzaron con un proceso de XNUMXnm y luego migraron a un proceso de XNUMXnm, y su dispositivo funciona con una batería de tipo botón.

El modelado se realizó en Matlab, C++ y SystemC. MatchLib, también se utilizó una biblioteca SystemC/C++. PowerPro se utilizó para la optimización y estimación de energía. Los resultados en un filtro de muesca IIR DC mostraron que HLS tenía una reducción de área de alrededor del 40 %, en comparación con RTL escrito a mano.

Planean integrar más HLS en su infraestructura e investigar el uso de HLV. Es un desafío hacer que sus ingenieros centrados en RTL piensen en términos de algoritmos y que los ingenieros de SW piensen en descripciones de hardware.

Google, UCV

El tráfico de video ocupa hasta el 80 % de Internet, por lo que Google ha centrado su desarrollo de HW en una unidad de codificación de video (VCU). Aki Kuusela presentó la historia de la compresión de video: H.264, VP9, AV1, AV2. La transcodificación de video sigue un proceso desde el creador hasta el espectador:

Google desarrolló sus propios chips para esta tarea de transcodificación de video para obtener una implementación adecuada de H.264 y VP9, optimizados para la carga de trabajo del centro de datos, por lo que un enfoque de diseño HLS les permitió hacer esto rápidamente. Con una VCU de Google, un creador puede cargar un video de 1080p 30 fps a 20 Mbps, luego un espectador puede verlo a 1080p 30 fps usando solo 4 Mbps.

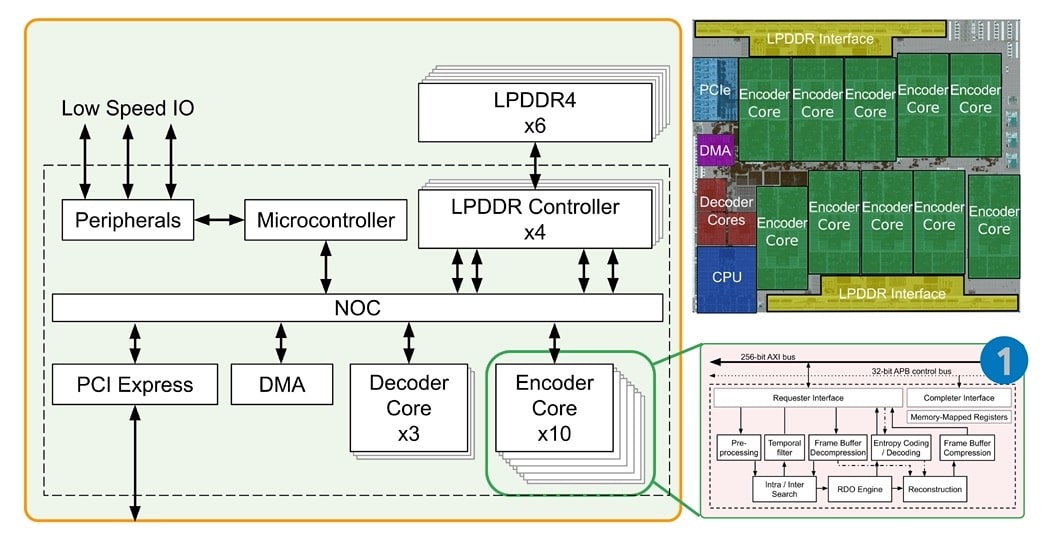

El diagrama de bloques VCU ASIC muestra cómo todos los bloques IP están conectados internamente a un NOC.

El VCU ASIC va a una placa y un bastidor, luego se construye en un clúster. Los ingenieros de Google han estado utilizando HLS durante aproximadamente 10 años y la metodología permite el codiseño SW/HW, además de una rápida iteración del diseño. Catapult convierte su C++ a Verilog RTL, y se utiliza una herramienta interna llamada Taffel para la integración, verificación y visualización de bloques.

El estilo de diseño HLS funcionó bien para bloques centrados en datos, máquinas de estado y árbitros. Con C++ había una única fuente de verdad y había resultados exactos en bits entre el modelo y RTL, utilizando de 5 a 10 veces menos código en comparación con la codificación RTL.

NVIDIA Research

Nate Pickney y Rangharajan Venkatesan comenzaron con cuatro áreas de investigación que HLS ha utilizado en su grupo: RC18: chip de inferencia, Simba: Inferencia de aprendizaje profundo con arquitectura basada en chiplet, MAGNET: Un generador acelerador modular para redes neuronales, IPA: Modelado de rendimiento de interconexión SystemC con reconocimiento de plano de planta.

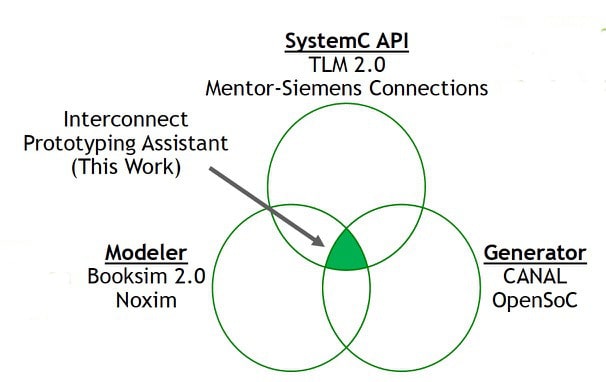

La motivación para IPA - Asistente de creación de prototipos de interconexión, fue abstraer y automatizar las interconexiones dentro de una base de código SystemC. Utiliza la API SystemC de IPA para el paso de mensajes mágicos, la simulación SystemC para el modelado y HLS para la generación de RTL. IPA fue desarrollado originalmente por NVIDIA y ahora es mantenido por Siemens EDA.

El flujo de diseño de SoC entre HLS y RTL, incluidas la exploración y la implementación, se muestra a continuación:

Agregar IPA a este flujo muestra cómo los tiempos de exploración se pueden reducir a 10 minutos, mientras que los tiempos de implementación son solo 6 horas.

Para el ejemplo del acelerador 4×4 MAGNET DL, el primer paso fue escribir un modelo SystemC unificado, realizar una ejecución inicial de la herramienta IPA, actualizar la interconexión y luego revisar la microarquitectura. Los experimentos de este análisis compararon enlaces conectados directamente, barra transversal centralizada y malla uniforme (NOC). Cada experimento que utilizó IPA tomó solo unos minutos de esfuerzo de diseño, en lugar de las semanas requeridas sin IPA.

La información de IPA es de código abierto, Obtenga más información aquí.

NVIDIA, códecs de vídeo

Hai Lin describió cómo su flujo de diseño y verificación sigue varios pasos:

- Especificaciones electrónicas de diseño HLS

- Comprobación de pelusa de diseño HLS

- Síntesis de catapulta eficiente

- Seguimiento de la calidad del diseño

- Optimización de energía, PowerPro

- Entrada de reloj a nivel de bloque

- Comprobación de coherencia HLS vs RTL

- Generación automática de banco de pruebas

- Inserciones de punto de cobertura de Cobertura de código de catapulta (CCOV)

Su grupo de códecs de video cambió de un flujo RTL a Catapult HLS y vio una reducción en el esfuerzo de codificación, una cantidad reducida de errores y tiempos de ejecución de simulación más cortos. La automatización ahora manejaba la canalización, la paralelización, la lógica de interfaz, la generación de señales inactivas y más. La sincronización del reloj RTL está automatizada con PowerPro. Finalmente, la metodología HLS integra código y cobertura funcional en el nivel de código fuente de diseño de C++.

STMicroelectronics

Los ingenieros de ST tienen 10 años de experiencia en HLS usando Catapult en productos como decodificadores, sistemas de imágenes y comunicación, y ahora están usando HLS para productos como: sensores, actuadores MEMS, ASIC para controladores de espejo MEMS y productos analógicos.

Un proyecto de sensor inteligente infrarrojo utilizó HLS y se entrenó una red neuronal a partir de un conjunto de datos provenientes de un sensor en situaciones de la vida real.

Con Catapult pudieron explorar redes neuronales con varios formatos aritméticos, luego comparar el área, la memoria y la precisión de los resultados. El tiempo para el diseño de HLS en Catapult, el análisis de datos, el banco de pruebas y el modelado fue de solo 5 semanas-persona.

Un segundo proyecto de diseño de HLS fue para un demodulador ASK compatible con Qi. Pudieron explorar el espacio de diseño comparando demoduladores con varias arquitecturas, luego midieron el área y los números de tiempo de holgura:

- Completamente enrollado

- Laminado parcial 8 ciclos

- Laminado parcial 4 ciclos

- Laminado parcial 2 ciclos

- Desenrollado

El tercer ejemplo compartido fue para un sensor infrarrojo sin contacto con procesamiento integrado. Se modelaron tres bloques HW para fórmulas de compensación de temperatura en HLS.

El RTL generado de cada bloque se ejecutó mediante síntesis lógica y los números de área se compararon para una variedad de arquitecturas. Los tiempos de latencia también se estimaron en Catapult para ayudar a elegir la mejor arquitectura.

JPL de la NASA

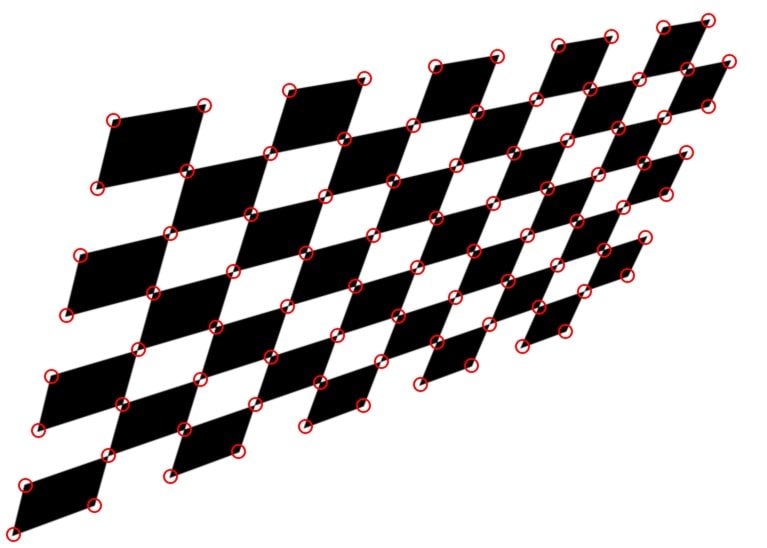

El ingeniero de FPGA Ashot Hambardzumyan de NASA JPL comparó el uso de C++ y SystemC para el Harris Corner Detector. El algoritmo principal calcula las derivadas Dx y Dy de una imagen, luego calcula una puntuación de respuesta de Harris en cada píxel y finalmente aplica una supresión no máxima a la puntuación.

Modelaron esto como un proceso DSP y la arquitectura HLS se modeló como un proceso Kahn. Se realizaron comparaciones entre el uso de enfoques C++, SystemC y SystemVerilog:

Para verificar cada uno de estos lenguajes se usó una imagen y se midió el tiempo de simulación por cuadro, y la implementación de SystemVerilog requirió 3 minutos por cuadro, SystemC tomó solo 5 segundos y C++ fue el más rápido con solo 0.3 segundos por cuadro.

Los tiempos de diseño y verificación para HLS fueron más cortos que con la metodología RTL. El entrenamiento básico para usar C++ fue más corto a las 2 semanas, en comparación con SystemC a las 4 semanas. El algoritmo Harris Corner Detector tomó solo 4 semanas usando C++, en comparación con 6 semanas con SystemC.

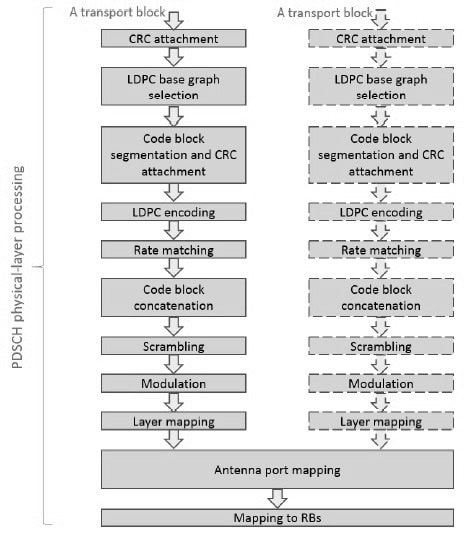

viosoft

La presentación final habló sobre 5G y los desafíos de la capa física (L1), donde se utilizan matemáticas complejas en la comunicación con algoritmos como estimación de canal, modulación, demodulación y corrección de errores de reenvío.

Se aplicó HLS a funciones L1 escritas en C++, luego se hizo una comparación en tiempo de ejecución para un CRC en tres implementaciones:

- CPU X86 XEON 2.3 GHz – 608, 423 ns

- CPU RISC-V QEMU de 2.3 GHz: 4,895,104 XNUMX XNUMX ns

- Catapulta – 300ns

Otra comparación fue entre un flujo de RTL versus flujo de Catapult para la frecuencia de reloj máxima, y mostró que los resultados de HLS de Catapult tenían una frecuencia de reloj 2 veces más alta que RTL. La utilización de recursos en dispositivos Intel FPGA mostró que RTL de Catapult era comparable a RTL manual en cuanto a utilización lógica, disipación de energía térmica total y disipación de energía térmica estática.

Viosoft prefiere la implementación de HLS de una sola fuente, ya que HW/SW se puede particionar más fácilmente, se pueden explorar las compensaciones de diseño, se puede estimar el rendimiento y se acorta el tiempo de comercialización.

Resumen

HLS y HLV son tendencias crecientes y espero ver una adopción continua en una lista cada vez mayor de áreas de aplicación. Los niveles más altos de abstracción tienen beneficios como menos líneas de código fuente, tiempos más rápidos para la simulación, verificación más rápida, todo lo cual deja más tiempo para la exploración arquitectónica. La codificación RTL no está desapareciendo, solo se está volviendo más eficiente con la automatización HLS.

Incluso hay IP de código abierto HLS en Github para ayudarlo a comenzar más rápido. La herramienta Catapult viene con ejemplos de referencia en diferentes aplicaciones para acelerar el aprendizaje. Incluso encontrarás YouTube tutoriales sobre el uso de HLS en Catapult. Él Libro azul de HLS es otra manera de aprender esta metodología.

ver los dos dias archivo de eventos aquí, unas 8 horas de vídeo.

Blogs relacionados

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- Platoblockchain. Inteligencia del Metaverso Web3. Conocimiento amplificado. Accede Aquí.

- Fuente: https://semiwiki.com/eda/321295-an-update-on-hls-and-hlv/