Chiplet se están convirtiendo rápidamente en los medios para superar la desaceleración de La Ley de Moore, pero aún no está claro si una interfaz es capaz de unirlos a todos. Universal Chiplet Interconnect Express (UCIe) cree que funcionará, pero algunos en la industria siguen sin estar convencidos.

Al menos parte del problema es que los estándares de interconexión nunca están realmente terminados. Incluso hoy en día, los protocolos que impulsan Internet (TCP/IP) siguen evolucionando. Surgen nuevas tecnologías, materiales y conceptos de empaque que requieren que los estándares sean lo suficientemente flexibles para evolucionar con el tiempo a fin de satisfacer las necesidades de todos los actores de la industria, incluidos los proveedores de propiedad intelectual, los diseñadores, las fundiciones y los empaquetadores.

UCIe 1.0 se lanzó el 2 de marzo de 2022 y, en ese momento, los objetivos iniciales incluían una E/S física de matriz a matriz, la adopción de protocolos de alto nivel PCIe/CXL para un mercado de volumen a corto plazo y una estructura que permitiría una futura ampliación. Un aspecto importante fue que se consideraron todas las principales tecnologías de empaque: intercalador o puente de silicio, abanico RDL y sustrato orgánico o laminado.

La Ley de Moore es fundamentalmente la capacidad de aumentar económicamente el número de transistores dentro de un paquete. “Si analiza nuestra capacidad para reducir los transistores, nos vamos a topar con un muro debido a la física”, dice Nick Ilyadis, director senior de planificación de productos de Achronix. “Ser capaz de integrar la funcionalidad en 2D, 2.5D o incluso 3D será clave para llevarnos al siguiente nivel de rendimiento del procesador o del sistema. La industria necesita una interconexión estandarizada que nos permita ampliar estos sistemas, no solo en un mundo 2.5D, sino también en un mundo 3D”.

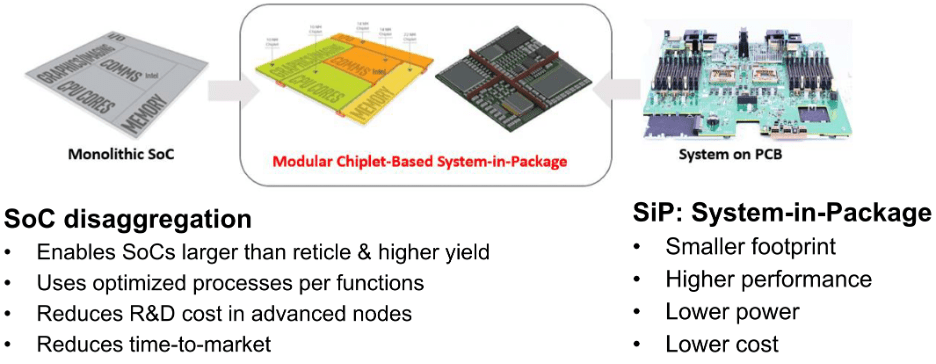

La continuación de la tendencia de integración significa tomar cosas que solían estar conectadas a nivel de placa y mover esa integración dentro del paquete. “Dentro del sistema y la placa de circuito impreso, intenta quitar los paquetes y colocar cada chip en el sustrato del paquete”, dice Ramin Farjadrad, fundador de Eliyan y desarrollador de Bunch of Wires (BoW). “Al hacer eso, se ahorra el costo de estos paquetes y se resuelve el problema del ancho de banda entre estos chiplets, porque pueden tener un ancho de banda muy alto entre ellos (ver figura 1). Eso se traduce en más rendimiento. Pero necesitamos tener una conectividad de matriz a matriz muy eficiente entre estos chipsets, como si estuvieran sentados en el mismo chip”.

Fig. 1: Principales casos de uso de la tecnología de chiplets. Fuente: Elián

Otras empresas se ven limitadas por el tamaño de la retícula y se ven obligadas a utilizar múltiples troqueles. “La mayoría de las implementaciones de troquel a troquel están, y seguirán estando, dirigidas a la conectividad entre diseños del mismo proveedor”, dice Guillaume Boillet, director senior de gestión de productos para IP de Arteris. “Bajo este escenario, se pueden construir soluciones más livianas y personalizadas en torno a una solución simple como 112G XSR u OpenHBI y BoW para menor paso y consumo de energía”.

El lanzamiento de UCIe no fue perfecto. “Uno de los problemas con el lanzamiento fue el mensaje sobre CXL y PCIe”, dice Mick Posner, director senior de HPC IP en Sinopsis. “Eso dejó a varias personas en el mercado con la idea de que UCIe lleva mucho equipaje. Pero cualquiera que haya leído la especificación ve que hay múltiples capas definidas en la especificación. Hace que UCIe sea aplicable a múltiples casos de uso, no solo al caso de uso en el que se utilizaría una conexión CXL o PCIe además”.

Aquí es donde 'universal' a menudo se interpreta como 'maestro de nada'.

“UCIe adoptó el enfoque de la máxima interoperabilidad sacrificando todo lo demás”, dice Elad Alon, cofundador y director ejecutivo de Blue Cheetah y profesor adjunto en UC Berkeley. “Tomaron esta noción de PCIe, PCB de las cosas, y trataron de forzar eso en el espacio de los chiplets. Se agregó una gran cantidad de gastos generales, que en la gran mayoría de los casos no son necesarios. Más importante aún, excluye a segmentos importantes del mercado general de participar debido al costo. Por ejemplo, le prohibió usar paquetes con menos de un cierto número de capas. La máxima interoperabilidad se produce a expensas de las cosas que le importan a la gente, como el costo, el rendimiento, la complejidad, la potencia y cosas de esta naturaleza”.

Aún así, eso no es necesariamente del todo malo. “Los protocolos PCI y CXL tienen un legado que no es deseable para algunas aplicaciones”, dijo Manuel Mota, gerente senior de productos para UCIe IP en Synopsys. “Ahí es donde algunas personas se sorprenden. Pero no es la única forma de usarlo. El protocolo de transmisión es un excelente ejemplo. Permite implementaciones muy livianas y de muy baja latencia que extienden los cables de un tejido, en un SoC, a otro SoC, y eso cubre muchos de los casos de uso que vemos en el mercado. Es un paso en la dirección correcta para el ecosistema de los chiplets. Otros estándares e implementaciones propietarias no están permitiendo eso, al menos en esta etapa, porque no están completos, porque se basan en decisiones de implementación, en aspectos críticos que definen su funcionamiento”.

Ambas partes creen que el tiempo les dará la razón.

¿Qué es la UCIe?

Como la mayoría de los protocolos de comunicaciones, UCIe se divide en tres capas de pila:

- Capa fisica: Esta es la especificación eléctrica del paquete de medios. Incluye el transmisor y el receptor, así como un canal de banda lateral para permitir el intercambio de parámetros y la negociación entre dos troqueles. Eso incluye la lógica PHY, que implementa los algoritmos de inicialización, entrenamiento y calibración del enlace, así como la funcionalidad de prueba y reparación.

- Capa de adaptador de matriz a matriz: Esto define la funcionalidad de gestión de enlaces, así como el arbitraje y la negociación de protocolos. Se define la funcionalidad opcional de corrección de errores, que se basa en un CRC y un mecanismo de reintento.

- Capa de protocolo: se pueden definir varios protocolos, pero la versión 1.0 define PCIe, CXL y un protocolo de transmisión.

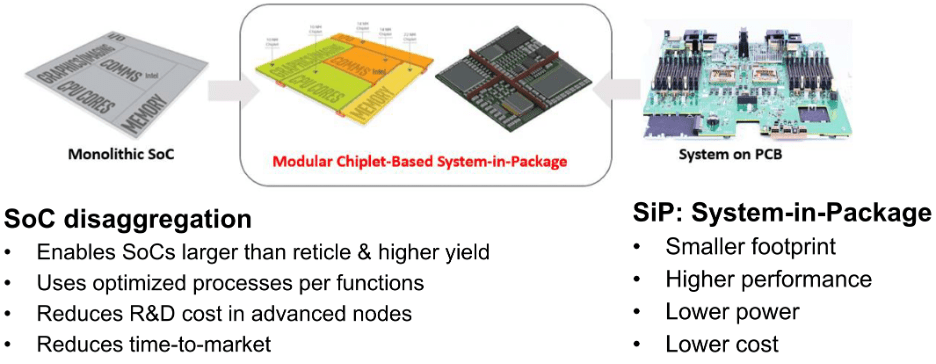

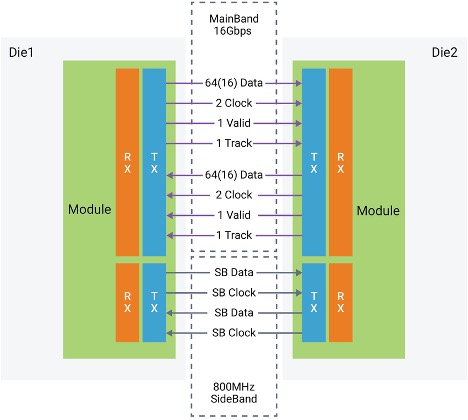

Es principalmente en la capa física donde otros estándares e implementaciones patentadas compiten con UCIe. UCIe utiliza reenvío de reloj y señalización DDR de bajo voltaje de terminación única (consulte la figura 2).

Fig. 2: Diagrama de bloques de la arquitectura UCIe PHY. Fuente: Sinopsis

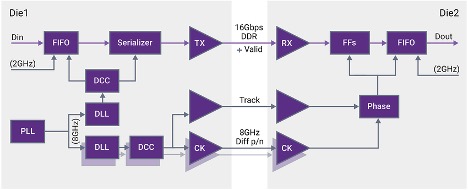

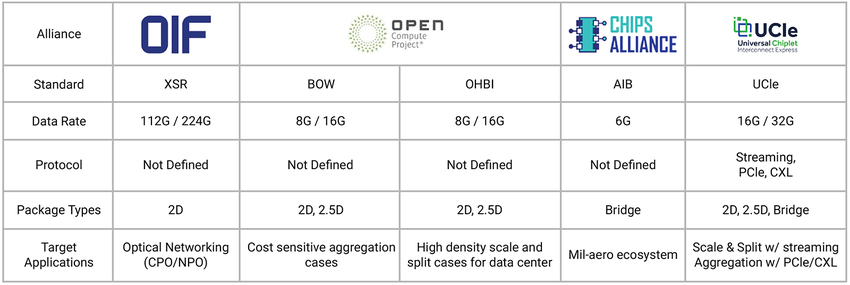

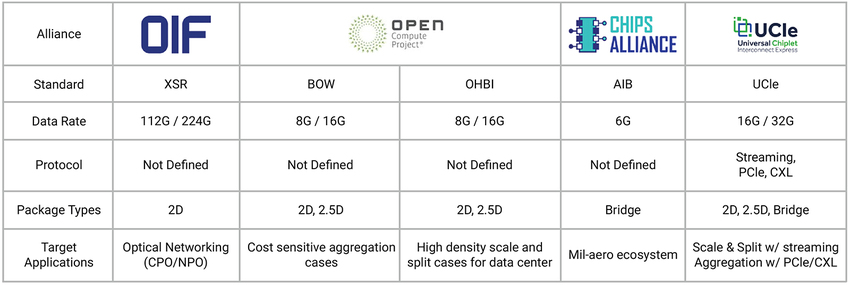

Muchos de los otros organismos de normalización han estado trabajando en esta capa durante un período de tiempo más largo, pero aún tienen que abordar los niveles más altos de la pila (consulte la figura 3).

Fig. 3: Alcance de los estándares de la capa física. Fuente: Sinopsis

De estos, Bunch of Wires es el más adelantado. “Bunch of Wires tiene un pequeño grupo de empresas que trabajan juntas para construir una familia de chips”, dice Ilyadis de Achronix. “Está un poco por delante de UCIe, porque tiene algunos tapeouts. Pero estaba un poco por delante de donde estaba el mercado, y muchas empresas se quedaron fuera del proceso de estándares cuando entró UCIe. Aspiraba el aire de la habitación para todo lo demás. UCIe será el superviviente a largo plazo, porque muchas empresas quieren tener una interoperabilidad garantizada”.

El trabajo en BoW ciertamente no se ha detenido. “Dentro de ODSA, hay un estándar de capa de enlace que está disponible en formato borrador y esperamos que pronto se apruebe formalmente”, dice Alon de Blue Cheetah. "Aborda específicamente el problema de cómo tomar múltiples NoC en matriz y conectarlos de una manera razonablemente compatible, a través de múltiples chiplets, manteniendo la flexibilidad".

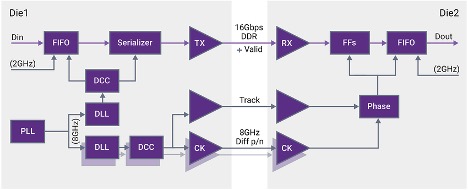

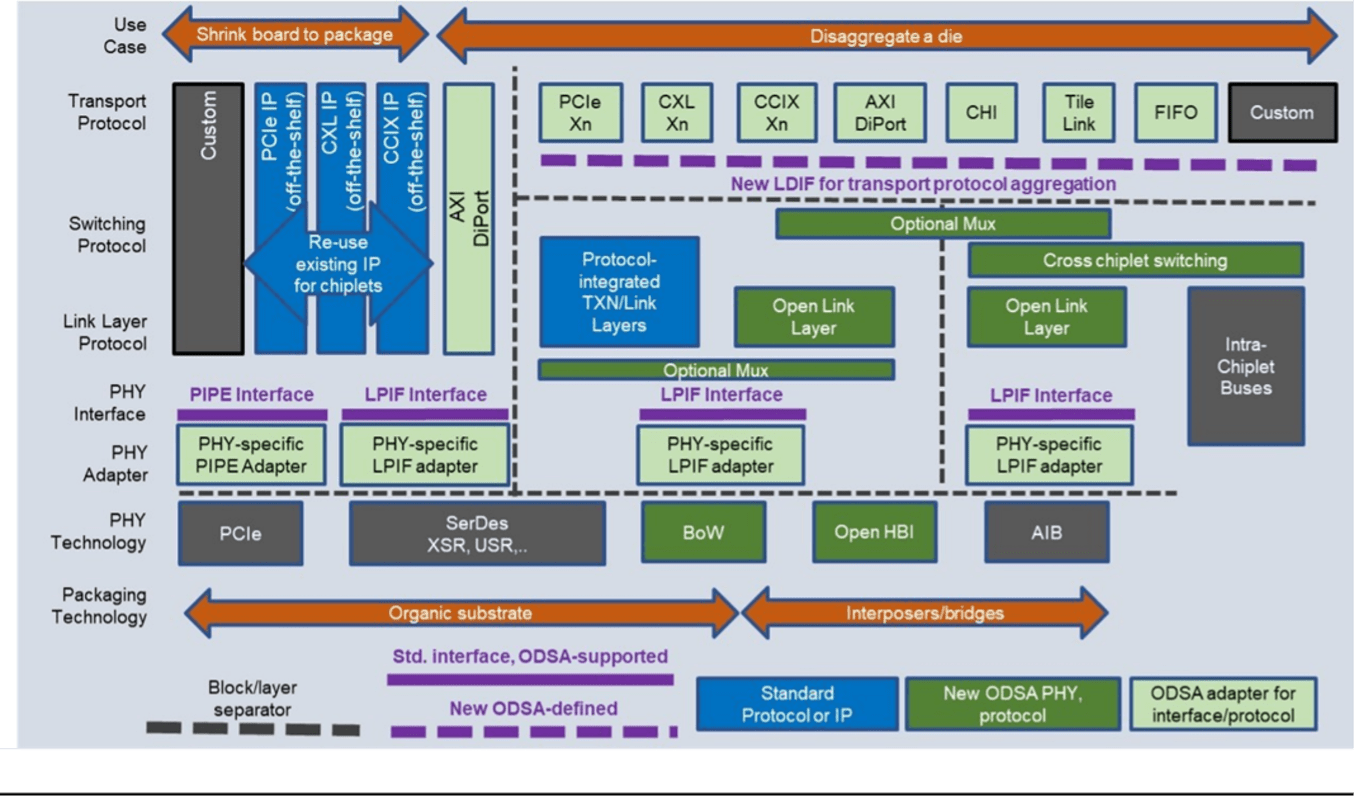

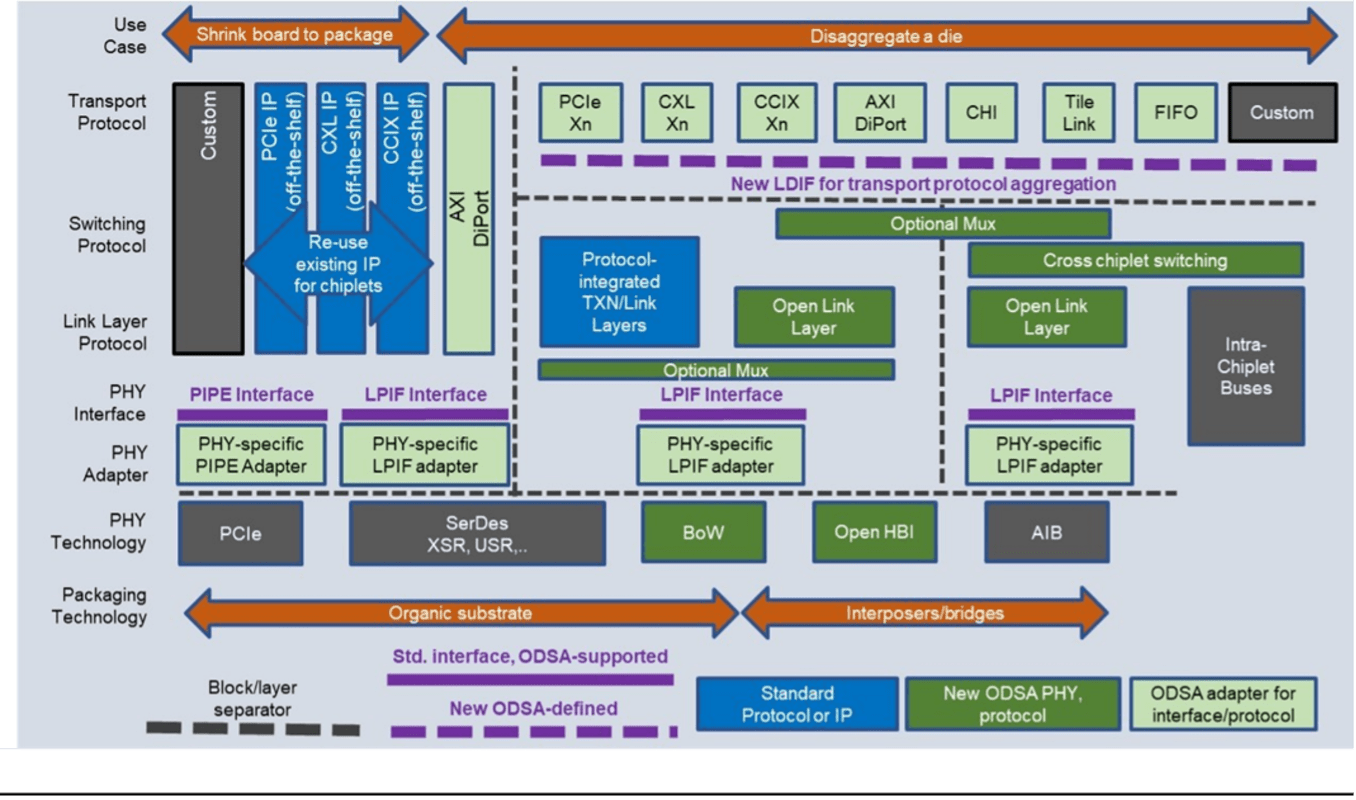

El componente lógico de la interfaz ODSA tiene como objetivo admitir protocolos utilizados para los dos casos de uso de chiplet más comunes, agregación de paquetes y desagregación de troqueles, en una amplia gama de PHY D2D abiertos y patentados, como PCIe, CXL, CCIX, AXI y propietarios. protocolos de transmisión (consulte la figura 4).

Fig. 4: Pila de comunicaciones en capas ODSA. Fuente: ODSA

Las empresas ya están intentando crear PHY que puedan adaptarse a ambos estándares e incluso ampliarlos. “Tenemos un PHY que es retrocompatible con UCIe”, dice Farjadrad de Eliyan. “Podemos hacer que opere con UCIe PHY para aplicaciones que lo necesiten. Pero vamos más allá de UCIe, y podemos tener comunicaciones bidireccionales simultáneas. Eso le da a cada cable una ventaja 2X sobre UCIe. Podemos proporcionar un rendimiento similar al de los envases avanzados, pero hacerlo con un sustrato orgánico”.

Otras empresas van en la dirección opuesta. "Tenemos clientes que actualmente usan BoW y solicitan compatibilidad con versiones anteriores porque quieren ir a UCIe", dice Sue Hung Fung, gerente de marketing de línea de productos para UCIe en Cadencia. “BoW tenía mucha popularidad, pero estamos viendo miembros que se han pasado a UCIe en su lugar. Esperamos que HBI entre en latencia. Otra comparación es AIB, que fue diseñado originalmente para EMIB. En la especificación de UCIe, Sección C, se mencionan planes futuros para implementaciones para diseñar un PHY interoperable de UCIe AIB”.

Convergencia a más largo plazo

En última instancia, todos estos grupos de estándares se dirigen hacia un objetivo similar, que es admitir varias capas de enlace y protocolos que operan sobre PHY de alto rendimiento. “UCIe, en su forma actual, no es una interfaz ideal de morir a morir porque básicamente toma los protocolos que se ejecutaban en las jaulas de tarjetas (tarjetas PCIe) y los reduce a una interfaz de morir a morir”, dice Ilyadis. “Esto está bien si está colocando periféricos alrededor de un procesador. Pero si está tratando de construir un sistema desagregado, entonces necesita algunos protocolos de nivel inferior que sean compatibles con la capa de enlace de datos, y específicamente los protocolos Arm AMBA y cosas como CHI para lograr coherencia. Estos son los que utilizan los diseñadores de sistemas para tejidos en chip como AXI. Deben ser compatibles para permitirle desagregar realmente los dispositivos y mantener una interconexión de muy baja latencia entre ellos”.

Ese legado puede tener costos a largo plazo. “El PHY es básicamente algo que muxea un montón de bits y luego los demuxea en el otro lado”, dice Farjadrad. “Pero si desea seguir el protocolo exacto definido por UCIe, debe proporcionar ciertas señales de banda lateral (consulte la figura 5). Esas señales se han realizado de manera muy ineficiente y requieren cuatro señales de banda lateral más dos señales de estado adicionales: seis golpes para administrar un enlace. En BoW hacemos esto con solo un golpe adicional. No es un desafío agregarlos, pero afecta la eficiencia del mapa de relieve. Incluso si no los usa en los protocolos de nivel superior, aún debe incluirlos”.

Fig. 5: Señales de banda principal y banda lateral de UCIe. Fuente: Sinopsis

El viaje

Hoy en día, todos los que crean un paquete que incluye múltiples troqueles están diseñando todo. Tienen control total sobre la capa PHY y los protocolos que utilizan para las comunicaciones. Realmente no importa si se ajustan completamente a alguno de los estándares. Solo necesitan compatibilidad entre sus propios troqueles.

“El mercado objetivo de terceros es como el mundo ideal de Platón”, dice Ilyadis. “Ese es el punto donde tienes interoperabilidad, plug and play, entre dispositivos. Requiere tener una tecnología de empaque que sea más accesible. Debe democratizarse para que las empresas más pequeñas tengan acceso. Pero es un viaje”.

El estándar de comunicaciones es solo una pieza del rompecabezas. “Hay muchos problemas que uno tiene que resolver para dar como resultado un verdadero mercado de chiplets plug-and-play”, dice Alon. “¿Cuál es el golpe de salida para estos chiplets? ¿Cuál es la huella de cada chiplet? ¿Cuál es el paquete estándar que usa para cada uno de estos? ¿Cómo interactúan desde el punto de vista de la fuente de alimentación? ¿Cuál es la partición que quieres? Hay una larga lista de cosas para las que nadie tiene respuesta todavía y son preguntas difíciles”.

¿Cuánto tiempo tardará? “He hablado con mucha gente en varias conferencias”, dice Hung Fung de Cadence. “La respuesta general es que faltan varios años. Escuché a personas decir 5, escuché a personas decir incluso 10. UCIe se está moviendo tan rápido en este momento, desde su creación, que podría ser antes”.

Uno de los problemas que hay que superar es el de las pruebas de compatibilidad. “¿Cómo se obtienen chiplets de un proveedor que garantizan la interoperabilidad con el chiplet de otro proveedor? Eso requiere mucha simulación”, dice Ilyadis. “Y luego lo ensamblas y esperas que funcione, porque será difícil probarlo. Tiene que haber un mecanismo por el cual tenga visibilidad de las interfaces reales y pueda ver lo que está sucediendo. Esa capacidad de prueba, la verificación de morir a morir, es tan importante como verificar las entrañas de cualquiera de los dispositivos”.

Ese proceso está comenzando. “Cuando desarrollamos IP, también desarrollamos un chip de prueba”, dice Posner de Synopsys. “A través de ese desarrollo de chips de prueba, obtenemos una experiencia significativa en lo que se requiere para cumplir con el rendimiento. Realizamos una gran cantidad de análisis en varias topologías de interposición y configuraciones de enrutamiento. Ese es exactamente el tipo de conocimiento que las empresas construyeron cuando crearon interfaces propietarias en el pasado. Estamos tomando esa información y se convierte en parte de nuestros entregables de diseño como garantía”.

El hecho de que ahora se integren en el paquete agrega algunas complicaciones. “Siempre existirá el concepto de validación de silicio”, dice Mota de Synopsys. “Cualquier proveedor de IP de buena reputación construirá chips de prueba que incluyan múltiples troqueles, para que podamos hacer pruebas reales de silicio. Si bien esto es entre nuestros propios dados, también lo estamos haciendo más allá de nuestros propios dados. Estamos colaborando con otras empresas para intentarlo con ellas. Ese es el espíritu de lo que UCIe define como una prueba de interoperación. Va a ser un mini PlugFest dentro del paquete. Probablemente usará algo como un dado dorado, o un diseño de referencia, conectado a través de UCIe. Luego puede probar las interfaces de morir a morir. Esas pruebas deben incluir una gran cantidad de funciones para garantizar que le brinden una cobertura muy alta”.

Verdadera universalidad

¿Es UCIe 1.0 realmente universal? Lejos de ahi. Ha tomado un caso de uso único y ha definido un estándar que aborda los problemas de ese mercado. No ha mirado al mercado de consumo, donde los costos son un factor más importante, o donde puede ser necesaria la integración de troqueles analógicos y de RF. No ha abordado las necesidades de mercados como el de la automoción, que impone exigencias específicas a los semiconductores.

“Si observa una gran cantidad de IP que se ha desarrollado, apunta a 7nm, 5nm o incluso 3nm”, dice Ilyadis. “Esa no es la tecnología que usará para construir dispositivos analógicos. Esta es una interfaz de bajo voltaje con velocidades de reloj de 16 gigabits, y eso lo llevará a los nodos de vanguardia. Va a ser muy bueno para los sistemas digitales heterogéneos, pero no creo que te dé esa gama completa de chipsets”.

La IP disponible está rastreando a los usuarios actuales que están impulsando el estándar. “Lo que escuchas que las empresas hablan hoy en día es ir a velocidades más altas, impulsar las tasas de datos más altas, un ancho de banda muy alto”, dice Mota. “Pero tiene que separar eso de lo que definen los estándares y de lo que el estándar dicta que debe respaldar. En su implementación, debe habilitar la operación de baja frecuencia para que pueda interoperar con dispositivos que, por la naturaleza del nodo de proceso, no pueden ir a 60 megabit por segundo. Algunas cosas deben permanecer a velocidades de datos bajas. Pueden interoperar con estos circuitos”.

Hay otras cuestiones que se abordarán con el tiempo. Uno de esos problemas es causado por el alcance de la interconexión, tal como se define hoy en día para interponedores y puentes. “Las GPU queman varios cientos de vatios y pueden funcionar en caliente, entre 100 °C y 105 °C”, dice Farjadrad. “Pero la DRAM, que puede estar junto a ellos, no puede funcionar a altas temperaturas. Tiene que funcionar a 80° a 85°. Debido a esta diafonía de temperatura, están limitados en la velocidad a la que pueden operar”.

Conclusión

La combinación de múltiples troqueles en un paquete sigue siendo una tecnología que solo utilizan algunas de las compañías de semiconductores más grandes en la actualidad, pero se considera una de las esperanzas más brillantes para la continuación de la Ley de Moore. Las empresas de vanguardia que están forjando el camino a seguir tienen que resolver muchos problemas, especialmente si el objetivo final es el plug-and-play universal de chiplets entre proveedores.

Llegar allí requerirá muchos pasos pequeños, porque no es posible resolver el problema más grande en un solo sprint. Es probable que se definan muchas piezas, algunas basadas en soluciones heredadas que se sabe que funcionaron en el pasado, y es igualmente probable que este enfoque conduzca a soluciones que no son óptimas para todas las aplicaciones.

Nadie puede prever el futuro, y tratar de predecirlo suele ser una tontería. La industria tiene un historial exitoso de construir sobre el pasado, aunque se sabe que muchas de estas decisiones son muy subóptimas en la actualidad.

Contenido relacionado

UCIe: el marketing lo arruina de nuevo

La denominación de productos suele ser irracional, pero cuando se trata de estándares, se debe tener especial cuidado. A menudo no lo es.

Estandarización de interconexiones de chiplet

Por qué UCIe es tan importante para la integración heterogénea.

¿Qué es la UCIe?

La interoperabilidad de dispositivos habilita el mercado de sistemas de matrices múltiples.

- Coinsmart. El mejor intercambio de Bitcoin y criptografía de Europa.Haga clic aquí

- Platoblockchain. Inteligencia del Metaverso Web3. Conocimiento amplificado. Accede Aquí.

- Fuente: https://semiengineering.com/is-ucie-really-universal/