Definir si un dispositivo 2.5D es una placa de circuito impreso reducida para caber en un paquete, o un chip que se extiende más allá de los límites de un solo troquel, puede parecer una semántica complicada, pero puede tener consecuencias significativas para el éxito general. de un diseño.

Los chips planos siempre han estado limitados por el tamaño de la retícula, que es de unos 858 mm.2. Más allá de eso, los problemas de rendimiento hacen que el silicio sea antieconómico. Durante años, eso ha limitado la cantidad de elementos que podrían incluirse en un sustrato plano. Cualquier característica adicional debería diseñarse en chips adicionales y conectarse con una placa de circuito impreso (PCB).

El advenimiento de 2.5D La tecnología de embalaje ha abierto un eje de expansión completamente nuevo, permitiendo múltiples chiplets estar interconectados dentro de un paquete avanzado. Pero el punto de partida de este diseño empaquetado puede tener un gran impacto en cómo se ensamblan los distintos componentes, quién está involucrado, qué herramientas se implementan y cuándo.

Hay varias razones por las que el 2.5D está ganando terreno hoy en día. Uno es el costo. "Si se pueden construir chips más pequeños, o chiplets, y esos chiplets se han diseñado y optimizado para integrarse en un paquete, se puede hacer que todo sea más pequeño", afirma Tony Mastroianni, director de soluciones de embalaje avanzadas de Software de Siemens Digital Industries. “Y como el rendimiento es mucho mayor, eso tiene un impacto dramático en el costo. En lugar de tener un rendimiento del 50 % o menos para chips del tamaño de un troquel, se puede aumentar hasta el rango del 90 %”.

La interconexión de chips mediante una PCB también limita el rendimiento. "Históricamente, teníamos chips empaquetados por separado y luego colocados en PCB y conectados entre sí con algún enrutamiento", dice Ramin Farjadrad, director ejecutivo y cofundador de Eliyan. “Los problemas que la gente empezó a afrontar eran dobles. Una era que el ancho de banda entre estos chips estaba limitado al pasar por la PCB y luego por un número limitado de bolas en el paquete, lo que limitaba la conectividad entre estos chips”.

La diferencia clave entre 2.5D y una PCB es que 2.5D utiliza dimensiones de chip. Hay cables de grano mucho más fino y varios componentes se pueden empaquetar mucho más juntos en un intercalador o en un paquete que en una placa. Por esas razones, los cables pueden ser más cortos, puede haber más y el ancho de banda aumenta.

Eso afecta el rendimiento en múltiples niveles. "Como están tan cerca, no hay grandes retrasos en el transporte RC o LC, por lo que es mucho más rápido", dice Mastroianni de Siemens. “No se necesitan controladores grandes en un chip para conducir pistas largas sobre el tablero, por lo que se tiene menor potencia. Obtendrá un rendimiento mucho mejor y menor potencia. Una métrica común es hablar de picojulios por bit. La cantidad de energía que se necesita para mover bits hace que el 2.5D sea atractivo”.

Aún así, la mentalidad afecta el concepto de diseño inicial y eso tiene repercusiones en todo el flujo. "Si hablas con un diseñador de troqueles, probablemente te dirá que se trata simplemente de un chip grande", dice John Park, director del grupo de gestión de productos del Custom IC & PCB Group de Cadencia. "Pero si hablas con un diseñador de paquetes o de placas, te dirán que es básicamente una PCB pequeña".

¿Quién tiene razón? "La estructura organizativa interna de la empresa a menudo decide cómo abordar esto", afirma Marc Swinnen, director de marketing de producto de Ansys. "A largo plazo, usted quiere asegurarse de que su empresa esté estructurada para igualar la física y no tratar de igualar la física de su empresa".

Lo que está claro es que nada es seguro. "El mundo digital era muy regular en el sentido de que cada dos años teníamos un nuevo nodo de la mitad del tamaño", dice Cadence's Park. “Habría algunos requisitos nuevos, pero fue muy evolutivo. El embalaje es el salvaje oeste. Podríamos obtener 8 nuevas tecnologías de envasado este año, 3 el próximo año y 12 el próximo año. Muchos de ellos provienen de las fundiciones, mientras que antes solo provenían de las empresas subcontratadas de ensamblaje y prueba de semiconductores (OSAT) y de los proveedores de sustratos. Si bien las fundiciones son nuevos participantes, los OSAT ofrecen algunas tecnologías de envasado realmente interesantes a un costo menor”.

Parte de la razón de esto es que diferentes grupos de personas tienen diferentes conjuntos de requisitos. "El gobierno y el ejército ven los principales beneficios como capacidades de integración heterogéneas", dice Swinnen de Ansys. “No están avanzando en la tecnología de procesamiento. En cambio, están diseñando cosas como circuitos integrados de microondas monolíticos (MMIC), donde necesitan guías de ondas para señales de muy alta velocidad. Lo abordan desde el punto de vista del montaje del embalaje. Por el contrario, las empresas de computación de alto rendimiento (HPC) lo abordan a partir de una pila de chips de 5 nm y 3 nm con memoria de alto ancho de banda (HBM) de alto rendimiento. Lo ven como un problema de ensamblaje del silicio. El beneficio que ven es la flexibilidad de la arquitectura, donde pueden incorporar núcleos e interfaces y crear productos para mercados específicos sin tener que rediseñar cada chiplet. Ven la flexibilidad como el beneficio. Los militares consideran que la integración heterogénea es un beneficio”.

Materiales

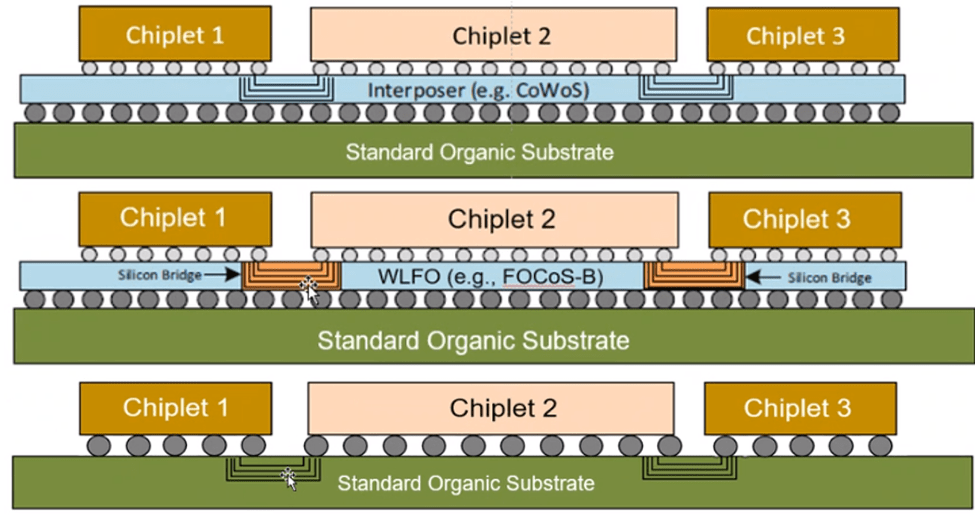

Hay varios materiales utilizados como sustrato en la tecnología de embalaje 2.5D, cada uno de los cuales tiene diferentes compensaciones en términos de costo, densidad y ancho de banda, además de una selección de diferentes problemas físicos que deben superarse. Uno de los principales puntos de diferenciación es el tono, como se muestra en la figura 1.

Fig 1. Interconexión de chiplets para varias configuraciones de sustrato. Fuente: Eliyán

Cuando se habla de un interpositor, generalmente se considera silicio. "El intercalador podría ser una gran pieza de silicio (Figura 1 arriba), o simplemente puentes de silicio entre los chips (Figura 1 central) para proporcionar la conectividad", dice Farjadrad de Eliyan. “Ambas soluciones utilizan microprotuberancias, que tienen una alta densidad. Los intercaladores y puentes proporcionan una gran cantidad de protuberancias y rastros de alta densidad, y eso le brinda ancho de banda. Si utiliza 1,000 cables, cada uno de los cuales funciona a 5 Gb, obtendrá 5 Tb. Si tienes 10,000, obtienes 50 Tb. Pero esas señales no pueden superar los dos o tres milímetros. Alternativamente, si evita el intercalador de silicio y se queda con un paquete orgánico (Figura 1 inferior), como un paquete de chip invertido, la densidad de las trazas es de 5 a 10 veces menor. Sin embargo, el grosor de los cables puede ser de 5 a 10 veces mayor. Esa es una ventaja significativa, porque la resistencia de los cables disminuirá en una proporción equivalente al cuadrado del grosor de los cables. La sección transversal de ese cable aumenta según el cuadrado de ese cable, por lo que la resistencia disminuye significativamente. Si tiene una densidad 5 veces menor, eso significa que puede transmitir señales casi 25 veces más lejos”.

Para algunas personas, todo se trata de ancho de banda por milímetro. "Si tiene un bus paralelo o una interfaz paralela de alta velocidad y desea un ancho de banda por milímetro, entonces probablemente elegiría un intercalador de silicio", dice Kent Stahn, gerente senior de ingeniería de hardware en Sinopsis'Grupo de Soluciones. “Un sustrato orgánico produce bajas pérdidas y es de bajo costo, pero no tiene la densidad necesaria. En el medio, hay un montón de soluciones que ofrecen algo de eso, pero no por el mismo costo”.

También existen otras razones para elegir un material de sustrato. "El intercalador de silicio proviene de una fundición, por lo que la disponibilidad es un problema", dice Manuel Mota, gerente senior de productos del grupo de soluciones de Synopsys. “Algunas empresas enfrentan desafíos a la hora de conseguir paquetes avanzados porque se ocupa la capacidad. Al optar por otras tecnologías que tienen un poco menos de densidad de ancho de banda, pero quizás suficiente para su aplicación, puede encontrarlas en otros lugares. Esto se está convirtiendo en un aspecto crítico”.

Sin embargo, todas estas tecnologías están progresando rápidamente. "El límite de la retícula es de aproximadamente 858 mm cuadrados", dice Park. “La gente habla de intercaladores que quizás sean cuatro veces más grandes, pero tenemos laminados que son mucho más grandes. Algunos de los sustratos laminados procedentes de Japón se están acercando al mismo nivel de densidad de interconexión que podemos obtener del silicio. Personalmente veo un mayor impulso hacia los sustratos orgánicos. Chip-on-Wafer-on-Substrate (CoWoS) de TSMC utiliza un intercalador de silicio y ha sido la tecnología elegida durante aproximadamente 12 años. Más recientemente, introdujeron CoWoS-R, que utiliza una película de poliamida, más cercana a un tipo de sustrato orgánico. Ahora escuchamos mucho sobre los sustratos de vidrio”.

Con el tiempo, el total de bienes inmuebles dentro del paquete puede crecer. “No tiene sentido que las fundiciones sigan fabricando cosas del tamaño de una placa de circuito impreso de 30 pulgadas”, añade Park. “Hay materiales que son capaces de abordar diseños más grandes. Donde realmente necesitamos densidad es en el morir a morir. Queremos esos chiplets uno al lado del otro, con un par de milímetros de longitud de interconexión. Queremos cosas muy cortas. Pero el resto es simplemente desplegar las E/S para que se conecten a la PCB”.

Por eso los puentes son populares. "Vemos una progresión hacia puentes para la parte de alta velocidad de la interfaz", dice Stahn de Synopsys. “La parte posterior sería en abanico, como el despliegue en abanico de RDL. Vemos paquetes RDL que en el futuro se parecerán más a paquetes tradicionales”.

Los intercaladores ofrecen capacidades adicionales. "Hoy en día, el 99% de los intercaladores son pasivos", afirma Park. “No hay un extremo frontal de la línea, no hay capas de dispositivos. Es puramente procesamiento final de línea. Estás agregando tres, cuatro, cinco capas de metal a ese silicio. Eso es lo que llamamos intercalador pasivo. Simplemente está creando esa interconexión de muerte a muerte. Pero hay gente que toma ese dado y lo convierte en un intercalador activo, básicamente añadiendo lógica a eso”.

Eso puede suceder con diferentes propósitos. "Ya se ven algunas empresas que utilizan intercaladores activos, donde agregan administración de energía o parte de la lógica de control", dice Mota. “Cuando empiezas a colocar circuitos activos en el intercalador, ¿sigue siendo una integración 2.5D o se convierte en una integración 3D? Hoy en día no vemos una gran tendencia hacia los intercaladores activos”.

Sin embargo, hay algunos problemas nuevos. "Hay que tener en cuenta los desajustes de los coeficientes de expansión térmica (CTE)", afirma Stahn. “Esto sucede siempre que se unen dos materiales con diferentes CTE. Comencemos con el intercalador de silicio. Puede obtener sistemas de mayor potencia, donde los SoC pueden comunicarse con sus pares y eso puede consumir mucha energía. Todavía falta incluir un intercalador de silicio en un paquete. Los desajustes de CTE se producen entre el silicio y el material del paquete. Y con el puente, lo estás usando donde lo necesitas, pero sigue siendo silicio de matriz a matriz. Tienes que hacer el análisis mecánico térmico para asegurarte de que la potencia que estás entregando y las discrepancias de CTE que tienes dan como resultado un sistema viable”.

Si bien en teoría la longitud de la señal puede aumentar, esto plantea algunos problemas. "Cuando se realizan esas conexiones largas dentro de un chip, normalmente se limitan esas rutas a un par de milímetros y luego se almacenan en un buffer", dice Mastroianni. “El problema con un intercalador de silicio pasivo es que no hay amortiguadores. Esto realmente puede convertirse en un problema grave. Si necesita hacer esas conexiones, debe planificarlas con mucho cuidado. Y debe asegurarse de ejecutar un análisis de tiempo. Por lo general, los encargados de su paquete no realizarán ese análisis. Se trata más bien de un problema que los ingenieros de silicio han resuelto con análisis de temporización estática. Necesitamos introducir un flujo STA y ocuparnos de todas las extracciones que incluyen trazas de tipo orgánico y de silicio, y se convierte en un nuevo problema. Cuando comienzas a entrar en algunas de esas trazas muy largas, tus simples retrasos de tiempo RC, que se suponen en las calculadoras de retardo STA normales, no tienen en cuenta parte de la inductancia y la inductancia mutua entre esas trazas, por lo que puedes tener serios problemas de precisión. por esas largas huellas”.

Los intercaladores activos ayudan. "Con los intercaladores activos, se pueden superar algunos de los problemas de larga distancia colocando buffers o repetidores de señal", dice Swinnen. “Luego empieza a parecerse más a un chip otra vez, y sólo se puede hacer con silicio. Tiene la tecnología EMIB de Intel, donde incorporaron un chiplet en el intercalador y ese es un puente activo. El chip se comunica con el chip EMIB, y ambos se comunican con usted a través de este pequeño chip puente activo, que no es exactamente un intercalador activo, pero actúa casi como un intercalador activo”.

Pero incluso los componentes pasivos añaden valor. "Lo primero que se está haciendo es incluir condensadores de zanja en el intercalador", dice Mastroianni. “Eso te da la posibilidad de hacer un buen desacoplamiento, donde sea necesario, cerca del dado. Si los coloca en el tablero, pierde muchos de los beneficios de las interfaces de alta velocidad. Si puedes colocarlos en el intercalador, ubicado justo debajo de donde tienes las señales de velocidad de conmutación rápida, puedes obtener un desacoplamiento localizado”.

Además de los diferentes materiales, está la cuestión de quién diseña el intercalador. "La industria parece verlo como un pequeño PCB en el contexto de quién hace el diseño", dice Matt Commens, gerente senior de gestión de productos de Ansys. “Los intercaladores suelen ser diseñados por ingenieros de embalaje, aunque sean procesos de silicio. Esto es especialmente cierto para los de alto rendimiento. Parece contradictorio, pero tienen experiencia en integridad de señal, han estado diseñando líneas de transmisión y minimizando los desajustes en las interconexiones. Un diseñador de circuitos integrados tradicional trabaja desde el punto de vista de los componentes. Ciertamente, la industria nos está diciendo que las personas que están asignando para hacer ese trabajo de diseño son personas del tipo empaque”.

Motor

Existen algunas diferencias considerables en el enrutamiento entre PCB e intercaladores. "El enrutamiento del interposer es mucho más sencillo, ya que el número de componentes se reduce drásticamente en comparación con la PCB", afirma Andy Heinig, jefe del departamento de electrónica eficiente de FraunhoferIIS/EAS. “Por otro lado, la red eléctrica en el intercalador es mucho más compleja debido a la mayor resistencia de las capas metálicas y al hecho de que la red eléctrica está cortada por cables de señal. El enrutamiento para la interfaz entre matrices es más complejo debido a la densidad de enrutamiento”.

La entrega de energía se ve muy diferente. "Si nos fijamos en una PCB, colocan estas grandes áreas de vertido de metal incrustadas en las capas y anulan las áreas por donde deben pasar las cosas", dice Park. “Dejas un montón de cobre y luego anulas los demás. No podemos construir un intercalador de esa manera. Tenemos que depositar la interconexión, para que las estructuras de alimentación y tierra en un intercalador de silicio se parezcan más a un chip digital. Pero la señal se parecerá más a una PCB o a un paquete laminado”.

El enrutamiento se parece más a una PCB que a un chip. "Verá cosas como lágrimas o filetes donde se conecta a una plataforma o vía para crear un mejor rendimiento", agrega Park. “Los estilos de enrutamiento actuales están más alineados con las PCB que con los circuitos integrados digitales, donde solo hay esquinas ortogonales de 90° y canales de enrutamiento limpios. Para los intercaladores, ya sean de silicio u orgánicos, la vía suele ser más grande que el cable, lo cual es un problema clásico de PCB. Los routers, si hablamos de digital, se parecen más a una pequeña PCB que a un troquel”.

Los TSV también pueden crear problemas. "Si los vas a tratar como cuadrados, estás perdiendo mucho espacio en las esquinas", dice Swinnen. “Lo que realmente quieres es un ángulo de 45° alrededor de esos objetos. Los enrutadores de silicio son tradicionalmente Manhattan, aunque existe una larga tradición de enrutamiento RDL, que es la capa superior donde se conectan los golpes. Tradicionalmente se han utilizado protuberancias octogonales o protuberancias redondas, y luego un recorrido de 45°. No es tan flexible como el enrutamiento de PCB, pero tienen enrutadores de capa de redistribución y también tienen algunos enrutadores que provienen del lado totalmente personalizado que tienen enrutamiento de río completo”.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiengineering.com/2-5d-integration-big-chip-or-small-pcb/