La búsqueda de tamaños de celdas DRAM cada vez más pequeños sigue activa y en curso. Se proyecta que el tamaño de celda DRAM se acerque a 0.0013 um2 para el nodo D12. Los desafíos de la creación de patrones son significativos, ya sea que se considere el uso de litografía DUV o EUV. En particular, ASML informó que cuando los valores de centro a centro alcanzaban los 40 nm, no se recomendaría un patrón único ni siquiera para EUV [1]. En este artículo, mostraremos que para el nodo DRAM de 12 nm y más allá, se espera que el condensador de centro a centro sea inferior a 40 nm, por lo que se requiere multipatrón.

Diseño de celda DRAM para capacitores de almacenamiento

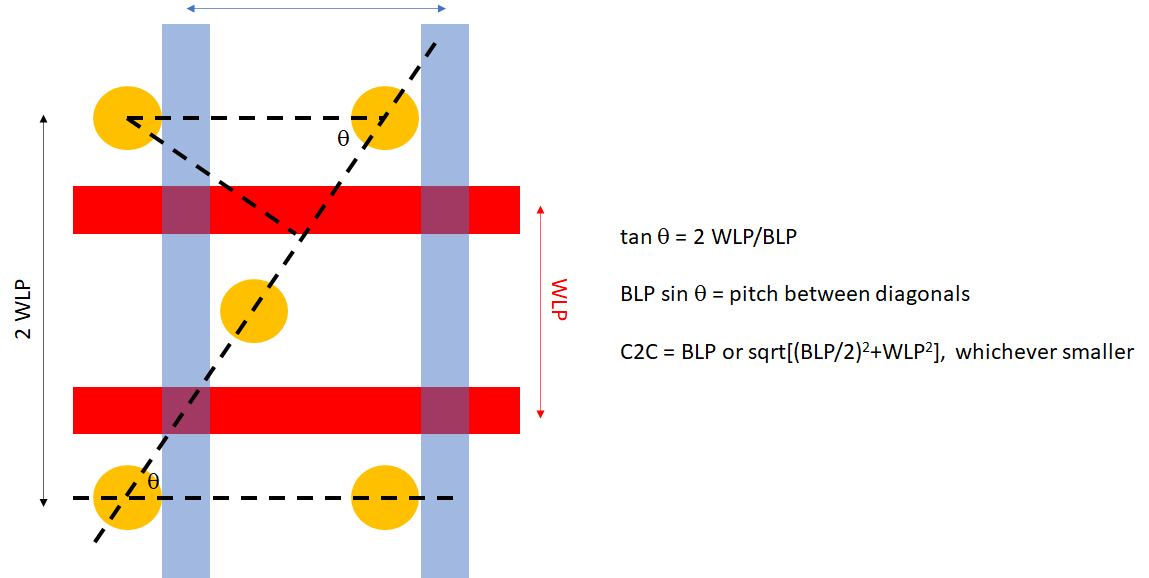

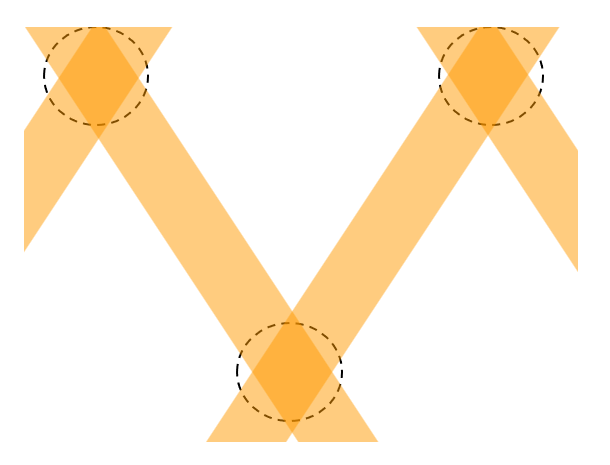

Los condensadores de almacenamiento están dispuestos en una matriz hexagonal (Figura 1). La regla de diseño del área activa está determinada por el paso de línea de bit y el paso de línea de palabra [2].

Figura 1. Nodos de almacenamiento (amarillo) en una cuadrícula de celdas DRAM. BLP=paso de línea de bit, WLP=paso de línea de palabra.

Un paso de línea de bit de 38 nm y un paso de línea de palabra de 33 nm daría lugar a un paso de centro a centro de 38 nm y un paso de 32.9 nm entre diagonales, para un tamaño de celda de 0.001254 um2 y una regla de diseño de área activa justo por debajo de 12 nm.

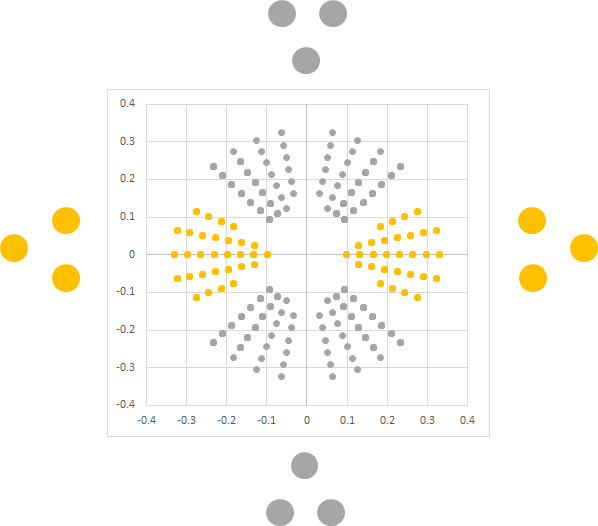

Para un sistema EUV de 0.33 NA, la matriz hexagonal usaría una iluminación hexapolar, donde cada polo produce un patrón de interferencia de tres haces (Figura 2). Los cuatro polos cuadrantes producen un patrón diferente al de los otros dos polos horizontales. Esto conduce a dos componentes de dosis separados con estocásticos separados. Estos se agregan en el patrón compuesto final.

Figura 2. La iluminación hexapolar para el patrón de almacenamiento DRAM consta de 4 polos de cuadrante (gris) y dos polos horizontales (amarillo). Dependiendo de la dirección de la iluminación, el patrón de interferencia de tres haces resultante tiene una orientación específica.

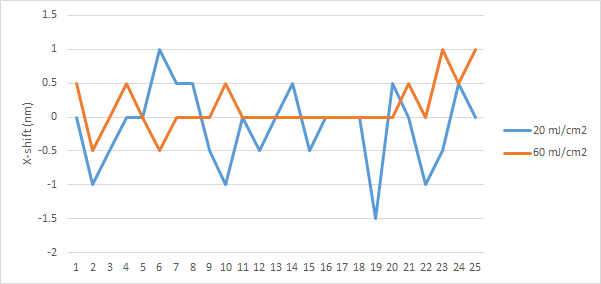

Debido al ruido sustancial del disparo de fotones absorbidos en el borde de la característica, el efecto estocástico en el error de colocación del patrón es significativo, como ya se describió en la Ref. 1, superando fácilmente una especificación de superposición de 1 nm. La dosis absorbida más baja parece ser obviamente peor (Figura 3).

Figura 3. Error de colocación estocástica (solo X) del pilar central en una celda unitaria de 38 nm x 66 nm (paso de línea de palabra = 33 nm), con la iluminación hexapolar esperada en un sistema EUV de 0.33 NA. Aquí se muestra una serie de 25 instancias diferentes para dos dosis absorbidas.

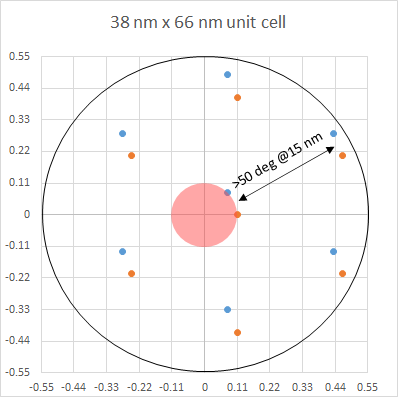

Ir a 0.55 NA agrega el problema de una profundidad de enfoque severamente reducida. Una NA de 0.55 daría como resultado un desenfoque de 15 nm que provocaría un cambio de fase de >50 grados entre los órdenes de difracción más interno y más externo (Figura 4), lo que reduce severamente el contraste de la imagen debido a la decoloración [3].

Figura 4. El desenfoque de 15 nm en un sistema EUV de 0.55 NA conduce a un cambio de fase de >50 grados entre los órdenes de difracción más interno y más externo.

Por lo tanto, es probable que el patrón del nodo de almacenamiento deba formarse a partir de dos patrones de líneas cruzadas (Figura 5). Cada patrón de líneas cruzadas puede estar formado por una exposición única EUV o por DUV SAQP (patrón cuádruple autoalineado). Ambas opciones son procesos de máscara única. El proceso SAQP es más maduro (habiendo precedido durante mucho tiempo a EUV) y libre de las preocupaciones estocásticas de electrones secundarios de EUV [4], por lo que debería preferirse. Aún así, para el caso de SAQP, las líneas espaciadoras deben estar bien controladas tanto en términos de ubicación como de rugosidad del ancho de línea [5].

Figura 5. El patrón del nodo de almacenamiento puede estar formado por la intersección de dos patrones de líneas cruzadas.

En lugar de SAQP de tipo línea, Samsung [2] también demostró un patrón de panal espaciador 6-D, utilizando una sola máscara con un patrón de panal inicial, en lugar de dos máscaras con patrones de línea inicial.

Si bien el caso anterior consideró un paso de línea de bit de 38 nm y un paso de línea de palabra de 33 nm, también se aplica al caso en el que se intercambian los pasos (paso de línea de bit de 33 nm y paso de línea de palabra de 38 nm), debido a la simetría hexagonal.

Referencias

[1] W. Gao y otros, Proc. SPIE 11323, 113231L (2020).

[2] F. Chen, Relación trigonométrica entre los tonos de las celdas DRAM, https://www.youtube.com/watch?v=Oq6b-6iw6Zk

[3] JH. Franke, TA Brunner, E. Hendrickx, J. Micro/Nanopattern. Mate. Metrol. 21, 030501 (2022).

[4] F. Chen, La aleatoriedad del desenfoque de electrones secundario como el origen de los defectos estocásticos de EUV, https://www.linkedin.com/pulse/secondary-electron-blur-randomness-origin-euv-stochastic-chen/

[5] N. Bae y otros, Proc. SPIE 11615, 116150B (2021).

[6] JM Park et al., IEDM 2015.

Este artículo apareció por primera vez en LinkedIn Pulse: Litografía específica de la aplicación: Sub-0.0013 um2 Patrón de nodo de almacenamiento DRAM

Lea también

Predicción de la densidad de defectos estocásticos EUV

Impacto de desenfoque de electrones en películas resistentes EUV de la reflexión de la interfaz

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- Platoblockchain. Inteligencia del Metaverso Web3. Conocimiento amplificado. Accede Aquí.

- Fuente: https://semiwiki.com/lithography/323357-application-specific-lithography-sub-0-0013-um2-dram-storage-node-patterning/