Para el Simposio de Estrategia Internacional SEMI 2024, los miembros del comité organizador me desafiaron a analizar dónde estará la lógica dentro de diez años desde una perspectiva de tecnología, economía y sostenibilidad. La siguiente es una discusión de mi presentación.

Para comprender la lógica, creo que es útil comprender qué constituye los dispositivos lógicos de vanguardia. TechInsights produce informes detallados de análisis de huella y tomé informes para diez dispositivos de clase de 7 nm y 5 nm, incluidos microprocesadores Intel y AMD, procesadores Apple series A y M, una GPU NVIDIA y otros dispositivos. La Figura 1 ilustra lo que constituye el área del troquel.

Según la figura 1, la lógica constituye un poco menos de la mitad del área del chip, la memoria un poco menos de un tercio del chip y las E/S, analógicas y otras, el resto. Me parece interesante que las áreas de memoria SRAM realmente medidas sean mucho más pequeñas que el porcentaje del que normalmente escucho a la gente hablar sobre los productos System On a Chip (SOC). El gráfico en la parte inferior derecha muestra que hay un valor atípico pero, por lo demás, los valores están muy agrupados.

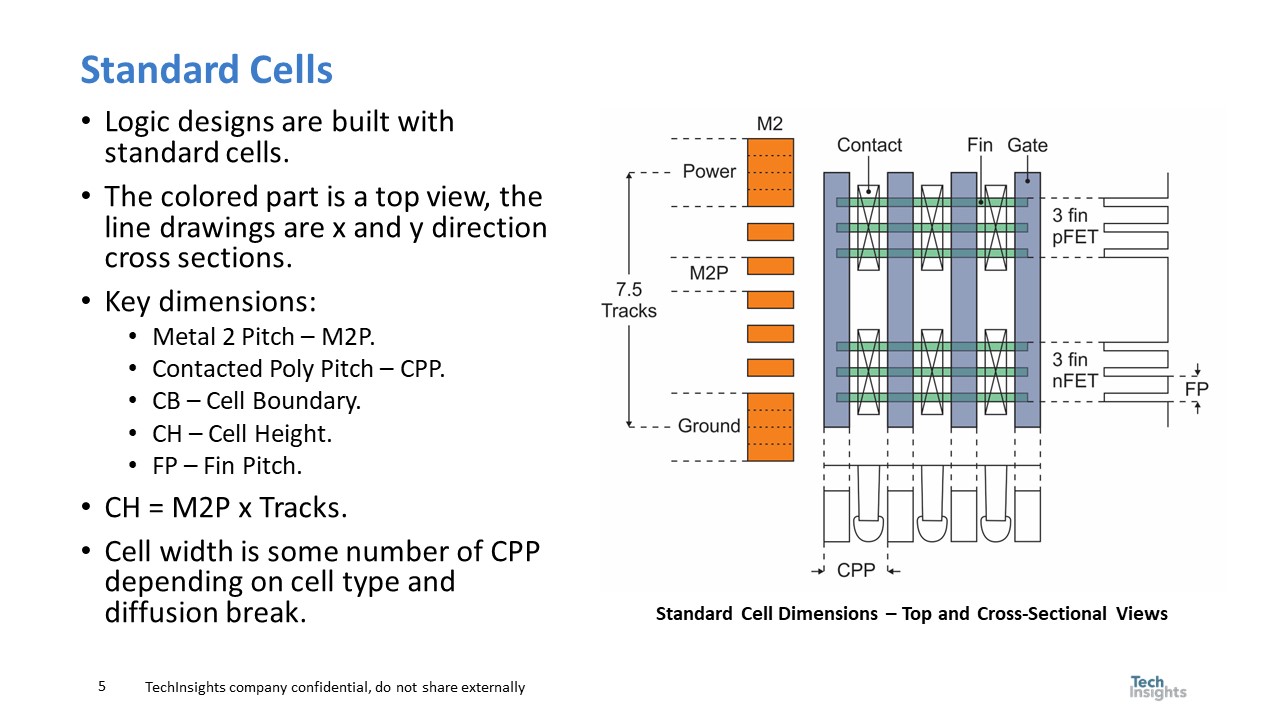

La lógica única ocupa casi la mitad del área del troquel, tiene sentido comenzar con la parte lógica del diseño. Los diseños lógicos se realizan con celdas estándar y la figura 2 es una vista en planta de una celda estándar.

La altura de una celda estándar generalmente se caracteriza como Metal 2 Pitch (M2P) multiplicada por el número de pistas, pero al mirar el lado derecho de la figura hay una vista en sección transversal de la estructura del dispositivo que también debe coincidir con la altura de la celda. y está limitado por la física del dispositivo. Lo mismo ocurre con el ancho de la celda que depende del Contacted Poly Pitch (CPP) y mirando en la parte inferior de la figura hay una vista en sección transversal de la estructura del dispositivo que una vez más está limitada por la física.

La Figura 3 presenta el resultado de un análisis para determinar los límites prácticos del escalamiento del ancho y la altura de la celda. Tengo una presentación que detalla las restricciones de escala y en esa presentación hay docenas de diapositivas entre la figura 2 y la figura 3, pero con tiempo limitado solo pude mostrar la conclusión.

La escala del ancho de celda depende del CPP, y el lado izquierdo de la figura ilustra cómo el CPP se compone de la longitud de la puerta (Lg), el ancho de contacto (Wc) y dos espesores del espaciador de contacto a puerta (Tsp). Lg está limitado por las fugas y el Lg mínimo con fugas aceptables depende del tipo de dispositivo. Los dispositivos planos con una sola puerta que controla la superficie de un canal con un espesor ilimitado están limitados a aproximadamente 30 nm. Los FinFET y las Nanosheets horizontales (HNS) limitan el espesor del canal (~5 nm) y tienen 3 y 4 puertas respectivamente. Finalmente, los materiales 2D introducen un espesor de canal <1 nm, materiales sin silicio y pueden producir Lg hasta ~5 nm. Tanto Wc como Tsp tienen una capacidad limitada de escalamiento debido a los parásitos. La conclusión es que un dispositivo 2D probablemente pueda producir un CPP de ~30 nm en comparación con los CPP actuales que son de ~50 nm.

La escala de altura de la celda se ilustra en el lado derecho de la figura. HNS ofrece pilas de nanohojas individuales en lugar de múltiples aletas. Luego, la evolución a dispositivos apilados con CFET elimina el espaciado horizontal de np y apila nFet y pFET. Las alturas de las celdas que actualmente oscilan entre 150 nm y 200 nm se pueden reducir a ~50 nm.

La combinación de CPP y el escalado de altura de celda puede producir densidades de transistores de ~1,500 millones de transistores por milímetro cuadrado (MTx/mm2) frente a los <300MTx/mm actuales2. Cabe señalar que los materiales 2D probablemente sean una tecnología de mediados a finales de 2030, por lo que 1,500 MTx/mm2 está fuera del momento discutido aquí.

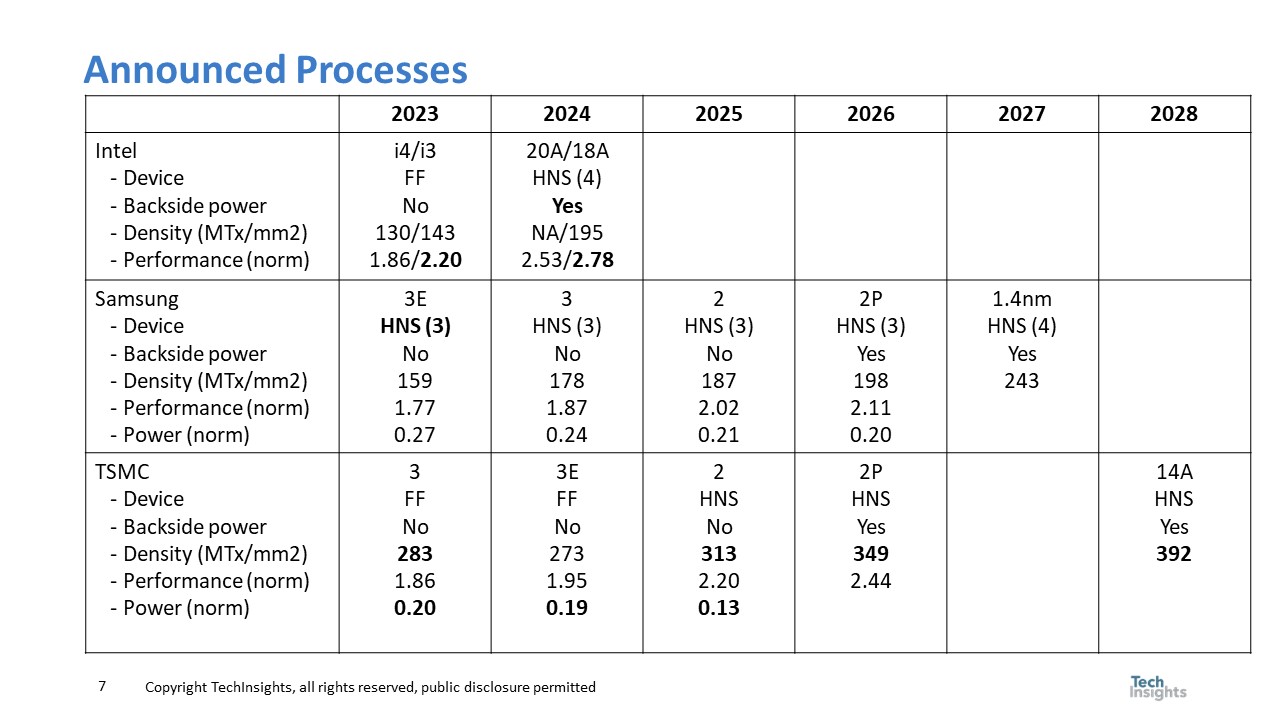

La Figura 4 presenta un resumen de los procesos anunciados por Intel, Samsung y TSMC.

Para cada empresa y año, se muestra el tipo de dispositivo, si se utiliza o no energía trasera, la densidad, la potencia y el rendimiento, si están disponibles. La potencia y el rendimiento son métricas relativas y la potencia no está disponible para Intel.

En la figura 4, las principales innovaciones tecnológicas y de rendimiento se destacan en negrita. Samsung es el primero en poner HNS en producción en 2023, donde Intel no introducirá HNS hasta 2024 y TSMC hasta 2025. Intel es el primero en introducir energía trasera en producción en 2024 y Samsung y TSMC no la introducirán hasta 2026.

Mi análisis concluye que Intel es el líder en rendimiento con i3 y mantiene ese estado durante el período ilustrado, TSMC tiene el liderazgo en energía (datos de Intel no disponibles) y liderazgo en densidad.

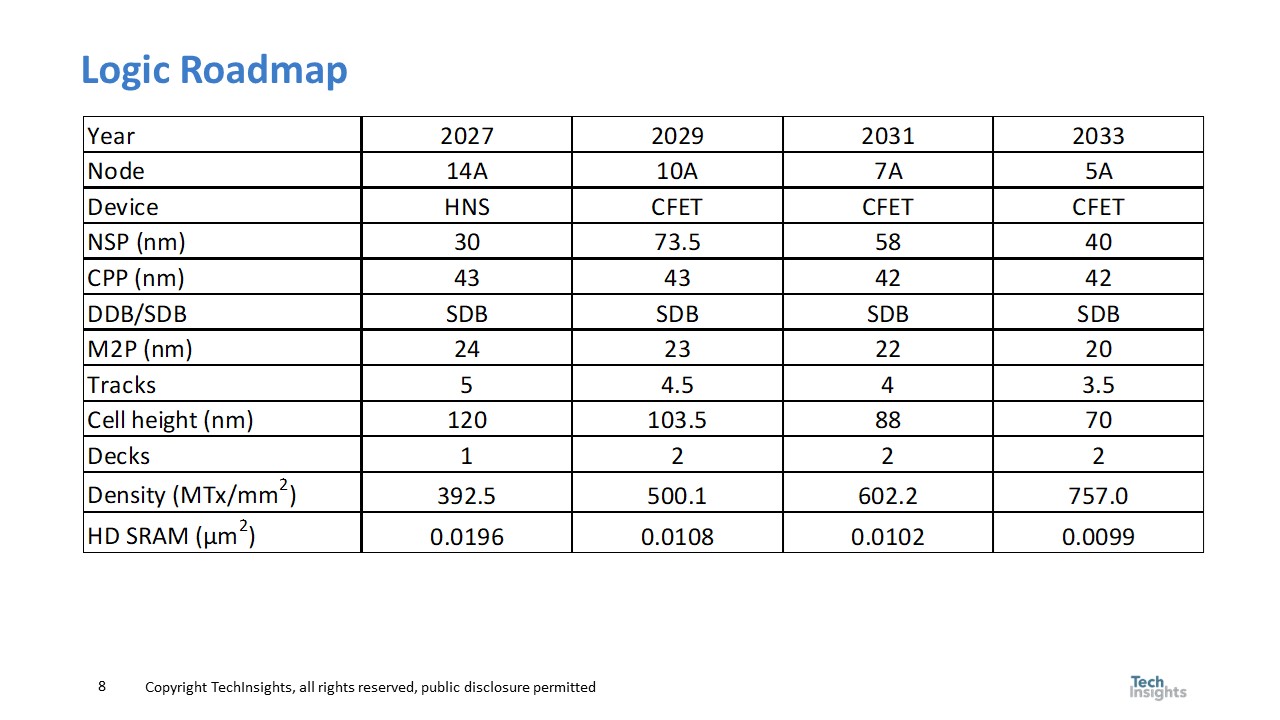

La Figura 5 presenta nuestras hojas de ruta lógicas e incluye tamaños de celda SRAM proyectados (más sobre esto más adelante).

Según la figura 5, esperamos que los CFET se introduzcan alrededor de 2029, lo que proporcionará un aumento en la densidad lógica y también reducirá el tamaño de las celdas SRAM casi a la mitad (el escalamiento del tamaño de las celdas SRAM prácticamente se ha detenido en el borde de ataque). Esperamos que la densidad lógica alcance ~757MTx/mm2 por 2034.

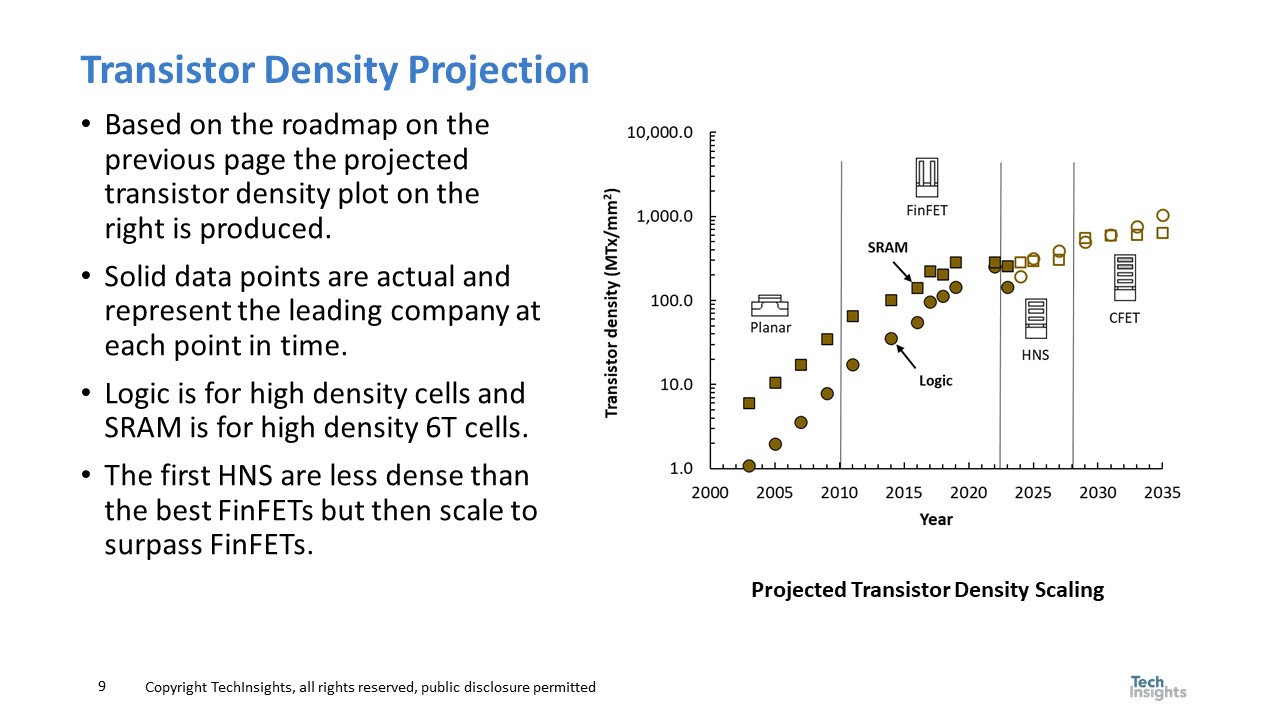

Tanto las proyecciones de densidad de transistores lógicos como las proyecciones de densidad de transistores SRAM se ilustran en la figura 6.

El escalado de densidad de transistores tanto lógicos como SRAM se está desacelerando, pero SRAM en mayor medida y la lógica ahora tiene una densidad de transistores similar a la SRAM.

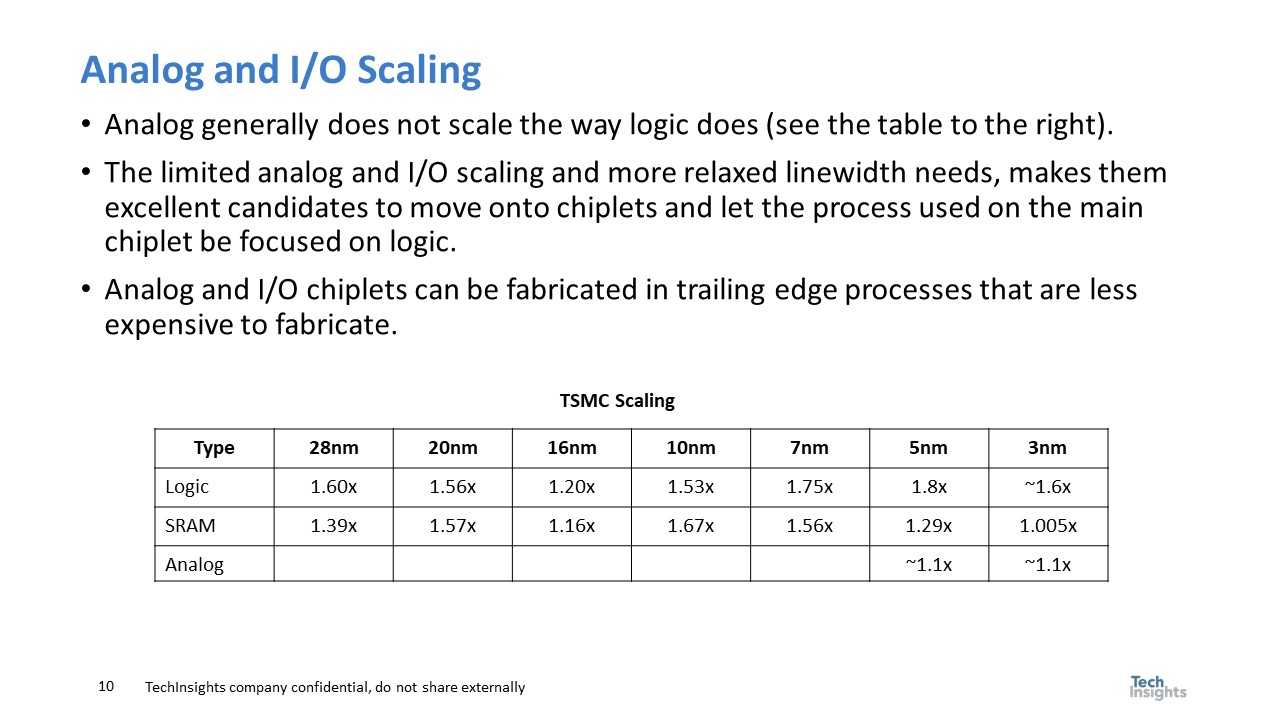

La diapositiva 7 resume los datos de TSMC sobre escalado analógico en comparación con Logic y SRAM. El escalado analógico y de E/S también son más lentos que el escalado lógico.

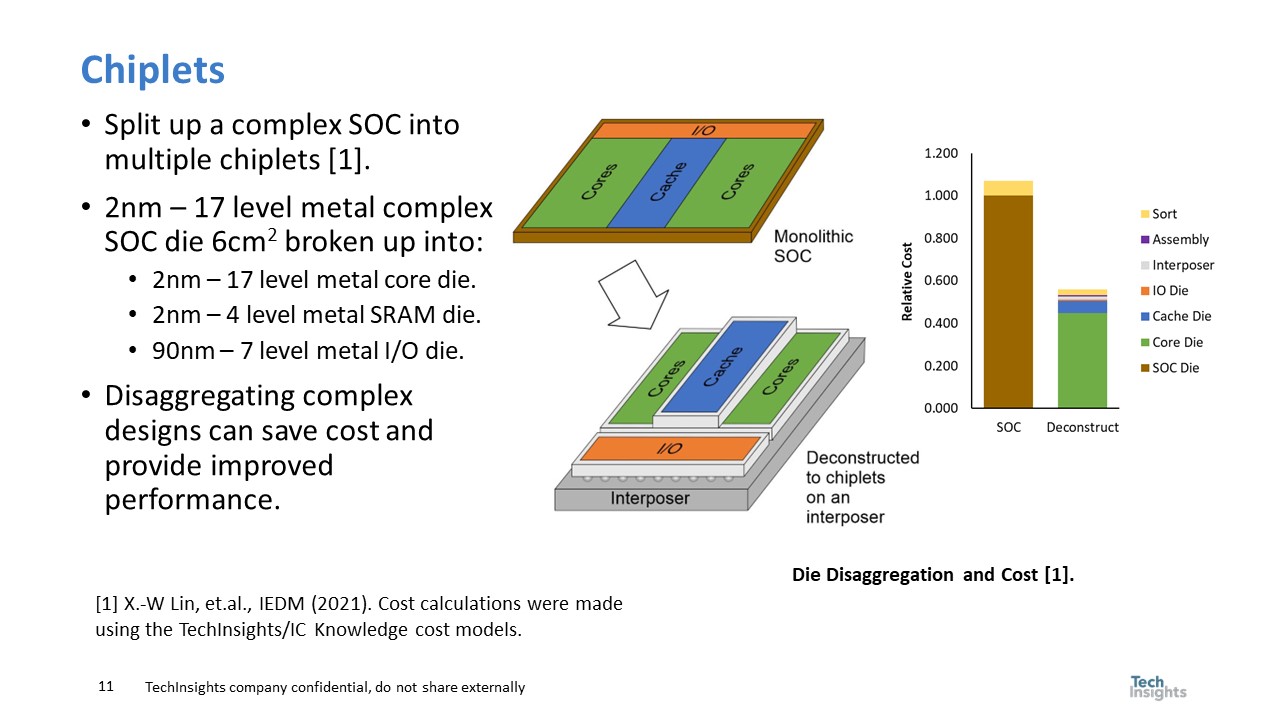

Una posible solución para una SRAM más lenta y un escalado analógico y de E/S son los chiplets. Los chiplets pueden permitir el uso de procesos menos costosos y más optimizados para crear SRAM y E/S.

La figura del lado derecho de la figura 8 proviene de un artículo de 2021 del que fui coautor con Synopsys. Nuestra conclusión fue que dividir un SOC grande en chips podría reducir el costo a la mitad incluso después de tener en cuenta el aumento de los costos de embalaje/ensamblaje.

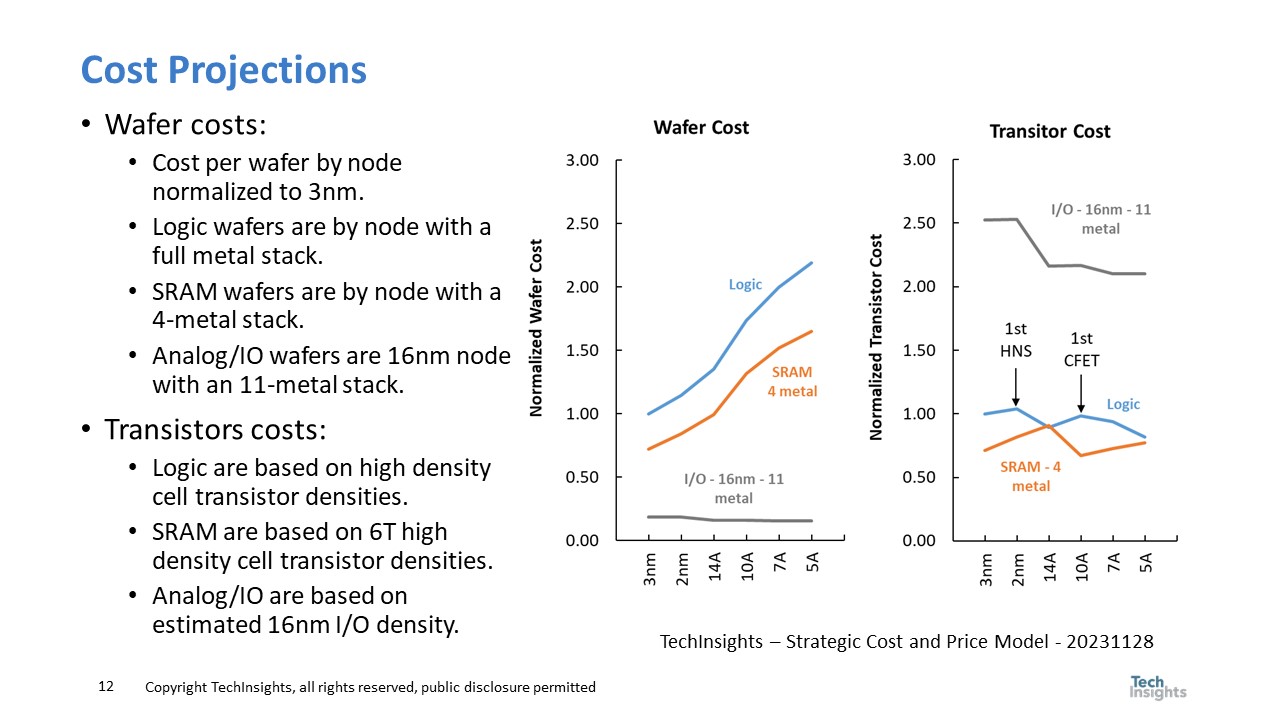

La Figura 9 presenta los costos normalizados de oblea y transistores para lógica, SRAM y E/S (tenga en cuenta que la figura se ha actualizado desde la presentación original).

En la figura de la derecha se muestra el costo normalizado de la oblea. El costo lógico de la oblea es para una pila de metal completa que aumenta en número de capas de metal. Las obleas SRAM son los mismos nodos pero limitadas a 4 capas metálicas debido al diseño más regular de SRAM. El costo de la oblea de E/S se basa en un proceso de 16 nm – 11 metales. Seleccioné 16 nm para obtener un nodo FinFET de costo mínimo para garantizar un rendimiento de E/S adecuado.

La cifra de la derecha es el costo de la oblea convertido al costo del transistor. Curiosamente, los transistores de E/S son tan grandes que incluso en una oblea de 16 nm de bajo costo tienen el costo más alto (el tamaño del transistor de E/S se basa en mediciones de TechInsights de transistores de E/S reales). Los costos de los transistores lógicos aumentan a 2 nm, el primer nodo de hoja TSMC HNS donde la contracción es modesta. Esperamos que la contracción en 14A sea mayor como nodo HNS de segunda generación (esto es similar a lo que hizo TSMC con su primer nodo FinFET). Una vez más, el coste del primer nodo CFET también aumenta el coste del transistor para un nodo. El costo del transistor SRAM tiende a aumentar debido a la contracción limitada, excepto por una contracción única del CFET. La conclusión de este análisis es que la reducción del costo de los transistores será modesta, aunque los Chiplets pueden proporcionar un beneficio único.

Pasando a la sostenibilidad, en la figura 10 se explican los diferentes “alcances” que componen la huella de carbono.

El alcance 1 son las emisiones directas del sitio debido a los químicos del proceso y la combustión (la electricidad también puede ser de alcance 1 si se genera en el sitio), el alcance 2 se debe a la huella de carbono de la electricidad comprada. El alcance 3 no está incluido en este análisis, pero se debe a la huella de carbono de los materiales comprados, el uso del producto fabricado y cosas como vehículos conducidos por empleados de una empresa.

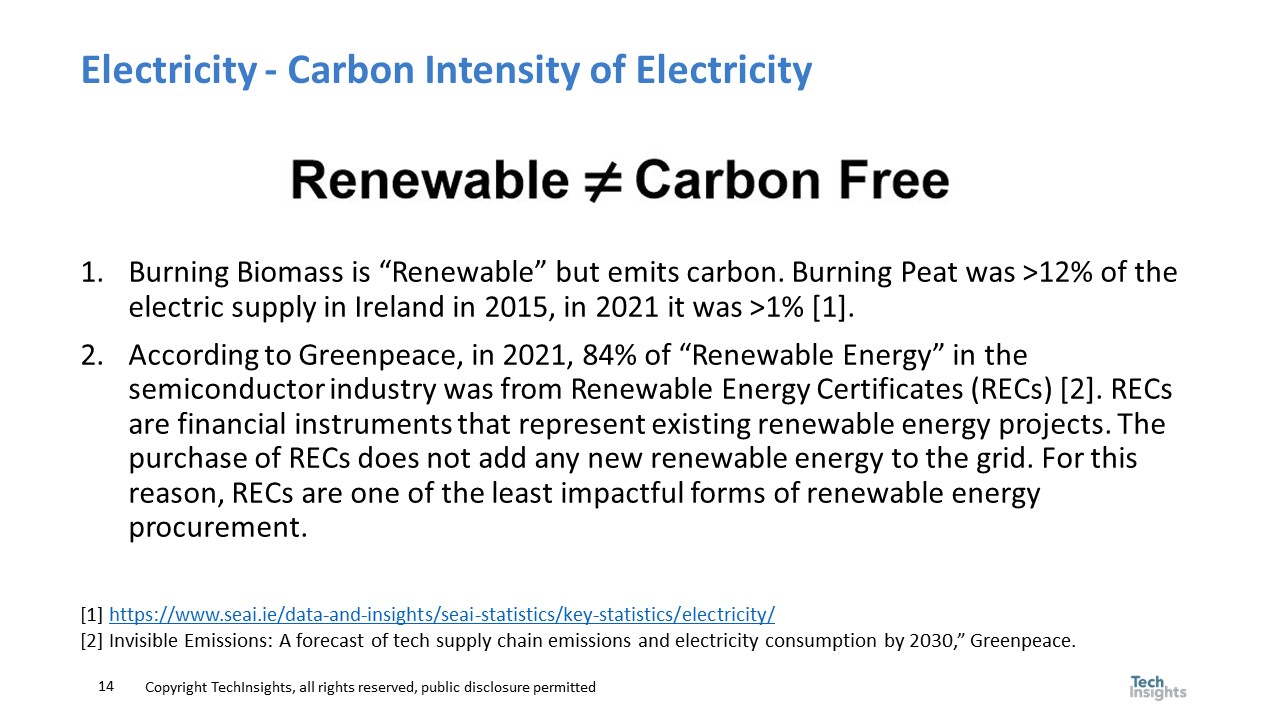

Muchas empresas de la industria de los semiconductores afirman que no tienen emisiones de carbono debido a la electricidad porque toda la electricidad es renovable. La Figura 11 compara las energías renovables con las libres de carbono.

El problema clave es que Greenpeace descubrió que el 84% de la energía renovable en la industria de los semiconductores en 2021 eran certificados de energía renovable donde una empresa compra los derechos para reclamar reducciones que otra ya hizo. Esto no es lo mismo que instalar fuentes eléctricas bajas en carbono o pagar a otros para que suministren electricidad baja en carbono y, de hecho, no reduce la huella de carbono global.

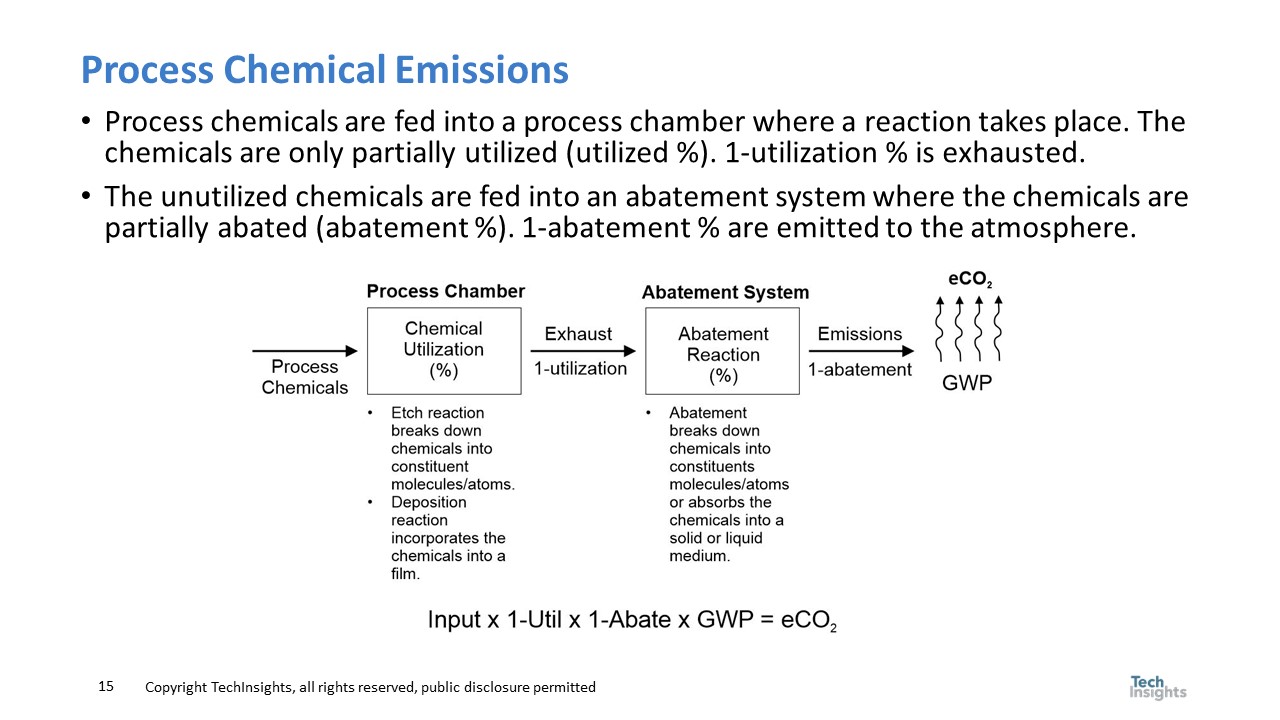

La Figura 12 ilustra cómo tienen lugar y se caracterizan las emisiones químicas del proceso.

Los químicos del proceso ingresan a una cámara de proceso donde un porcentaje de los químicos se utiliza en una reacción de grabado o deposición que descompone los químicos o los incorpora en una película depositada. 1-uitlización es la cantidad de producto químico que se escapa por el escape de la herramienta. Luego, el escape de la herramienta puede ir a una cámara de reducción, donde se descompone aún más un porcentaje de los productos químicos y las emisiones a la atmósfera a partir de la reducción son 1-reducción. Finalmente, se aplica un Potencial de Calentamiento Global (GWP) para calcular la equivalencia de carbono de la emisión. El GWP tiene en cuenta cuánto tiempo persiste la sustancia química en la atmósfera y cuánto calor refleja en comparación con el dióxido de carbono. El dióxido de carbono tiene un PCG de 1, los productos químicos de proceso de semiconductores como el SF6 y NF3 tienen valores de GWP de 24,300 y 17,400 respectivamente (según IPCC AR6).

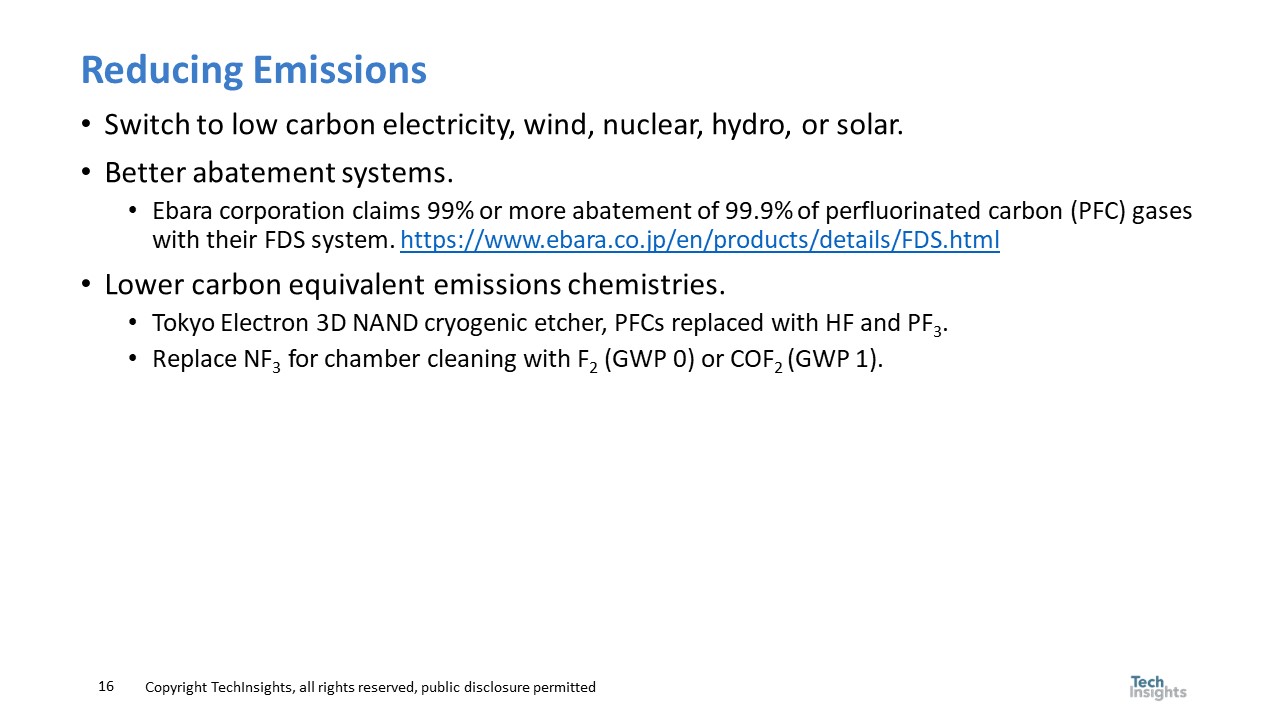

La Figura 13 presenta algunas opciones para reducir las emisiones.

Fuentes de electricidad como el carbón producen 820 gramos de CO2 emisiones equivalentes por kilovatio hora (gCO2e/KWh), mientras que la energía solar, hidroeléctrica, eólica y nuclear producen 48, 24, 12 y 12 gCO2e/KWh respectivamente.

Los sistemas de reducción más eficientes pueden descomponer los gases de proceso de manera más efectiva. La eficiencia de los sistemas de reducción fabulosos varía desde el 0 % para algunos sitios de EE. UU. informados (sin reducción) hasta ~90 %. Estimamos que el promedio mundial de fábricas de 300 mm es ~70 % y que la mayoría de las fábricas de tamaño de oblea de 200 mm y más pequeñas no tienen reducción. Hay disponibles sistemas con hasta un 99% de eficiencia.

También se puede utilizar una química de bajas emisiones. Tokyo Electron ha anunciado una nueva herramienta de grabado para 3D NAND que utiliza gases con cero GWP. Gases como SF6 y NF3 se utilizan principalmente para suministrar flúor (F) a las cámaras para su limpieza, sustituyendo el F2 (PCA 0) o COF2 (GWP 1) puede eliminar esencialmente esta fuente de emisiones.

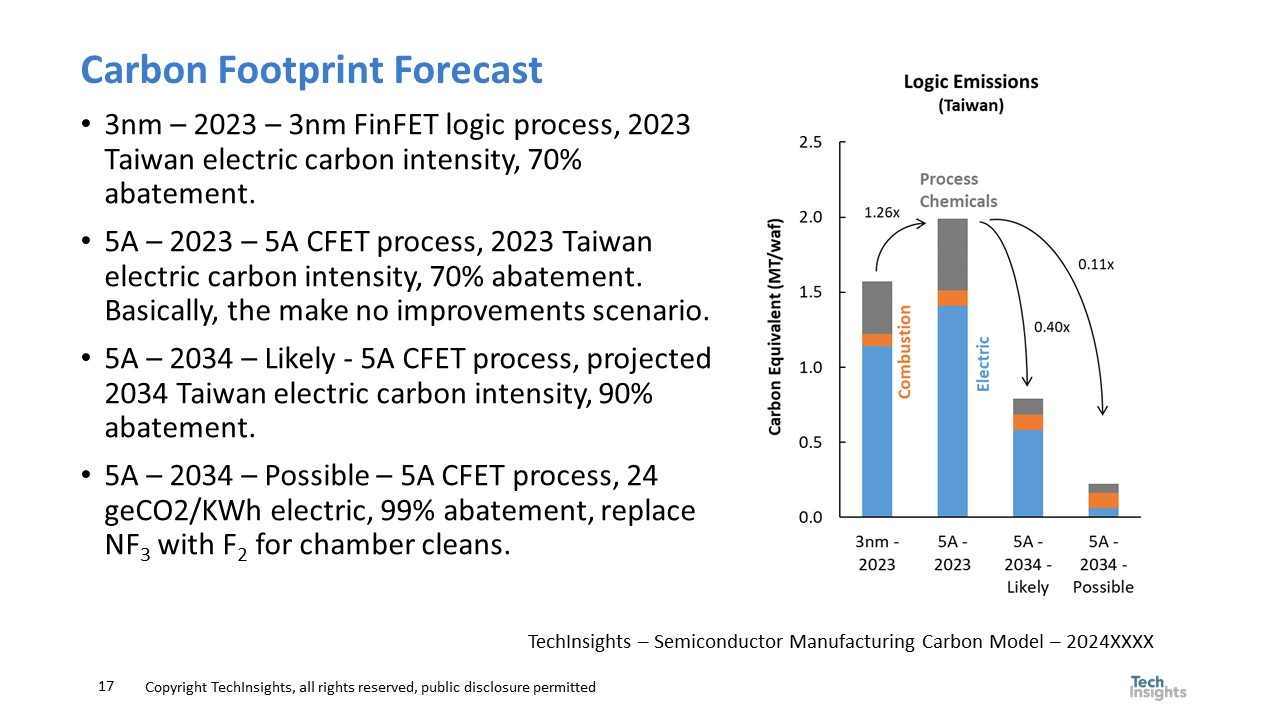

La Figura 14 ilustra un Pronóstico de Huella de Carbono por lógica.

En la figura, la primera barra de la izquierda es un proceso de 3 nm ejecutado en Taiwán en 2023, suponiendo la huella de carbono de la electricidad de Taiwán y una reducción del 70%. La segunda barra es un proceso 5A y la emisión que resultaría si se utilizara la misma intensidad de carbono de la electricidad de Taiwán de 2023 y una reducción del 70%. El aumento en la complejidad del proceso aumentaría la huella total en 1.26 veces. De cara al año 2034, se espera que la electricidad de Taiwán se descarbonice significativamente; además, una reducción del 90% debería ser común, y la tercera barra muestra cómo sería un proceso 5A bajo esta condición. Si bien esto representa una reducción de las emisiones a más de la mitad, el crecimiento en el número de obleas gestionadas por la industria para 2034 probablemente superaría esta mejora. La última barra a la derecha es lo que es posible con una inversión suficiente, se basa en electricidad baja en carbono, una reducción del 99% y el uso de F.2 para la limpieza de la cámara.

La Figura 15 presenta nuestras conclusiones:

La densidad de transistores y las estimaciones de costos de obleas y matrices se generaron utilizando el modelo de precios y costos estratégicos de TechInsights, una hoja de ruta de la industria que produce estimaciones de costos y precios, así como requisitos detallados de equipos y materiales. Las estimaciones de emisiones de GEI se produjeron utilizando el modelo de carbono de fabricación de semiconductores de TechInsights. Para obtener más información, comuníquese con sales@techinsights.com

Me gustaría agradecer a mis colegas de la Unidad de Negocios de Ingeniería Inversa de TechInsights, sus planos digitales e informes de procesos fueron de gran ayuda para crear esta presentación. Además, Alexandra Noguera de TechInsights por extraer datos de tamaño de transistores de E/S para este trabajo.

Lea también

IEDM 2023: Modelado de emisiones de carbono de fábricas de obleas de 300 mm

SMIC N+2 en Huawei Mate Pro 60

Actualización de ASML SEMICON Oeste 2023

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/semiconductor-manufacturers/342094-iss-2024-logic-2034-technology-economics-and-sustainability/